パネル加工における実績のある生産性能

世界中の生産ツール

- 最大650×650mmのパネル

- 310×310mmを含む新しいパネルサイズに対応するソリューション

「シード層」プロセス

- トレンチおよびビア用コンフォーマルコーティング

- 高アスペクト比プロセス

次世代IC基板およびチップレットパッケージ

- PVDプロセスにより二酸化炭素排出量を削減し、構造の小型化を実現

- 両面プロセスにおける基板反転機能

業界をリードする製造ソリューション

- 脱ガス、エッチング、PVDプロセスソリューション

- 最高のCoOを実現する、最低Rcと最高のスループット

ファンアウトパネルレベルパッケージングおよびアドバンスIC基板

ChatGPT やその他言語生成など新タイプのニューラル ネットワークと、さまざまな人工知能 (AI) アプリケーションにより、高性能コンピューティング (HPC) の需要がかつてないレベルにまで高まっています。チップレット パッケージ、新しい放熱方法、小型化、新材料の活用、電力最適化などのイノベーションが進歩するためにアドバンスパッケージングが重要な役割を果たすようになってきています。

高効率でと技術的優位性を備えたアドバンスパッケージングは、業界のロードマップをサポートする成長が著しい分野です。

310x310mmから650x650mmまで、革新と新しいチャンスに溢れたパネルレベルパッケージング

ケミカルシード層に代わるスパッタリング シード層は、さまざまな新しい可能性を実現します。次世代 IC 基板およびPCB基板などのOEM とメーカーは、ガラス コアとガラス貫通ビア (TGV) などの新しい材料をパッケージに統合する製造プロセスで、より小型かつ精密な構造、信頼性の向上、および二酸化炭素排出量の削減を可能にする技術としてスパッタリング シード層を採用しています。また、次世代チップレット パッケージの開発は、将来的に劇的な市場機会をもたらします。

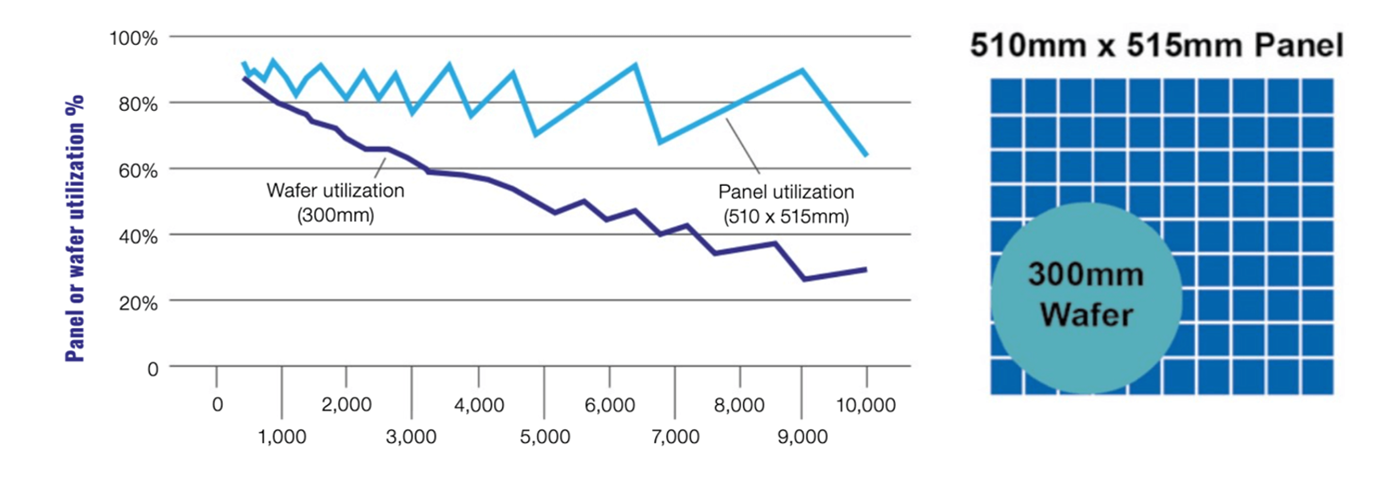

より多くのチップを 1 つのパッケージに統合するとパッケージのサイズが大きくなります。パッケージのサイズが大きくなると、円形のウェハーでの材料と装置の利用が非効率的になります。そのため、業界では、300 x 300 mm から 600 x 600 mm 寸法の長方形の基板を処理するパネル サイズの半導体レベルのプロセス装置へと移行しています。

Evatec は、さまざまな材料を使用したファンアウト パネルレベル パッケージングおよび高度な IC 基板用のパネルサイズの半導体グレード プロセス機器で市場をリードしています。業界最先端のEvatec の CLUSTERLINE® 600 プラットフォームは、最大 650 x 650 mm の基板サイズを処理し、ガス放出、シード層の接着、スタックの均一性において最高のパフォーマンスを実現します。

量産向け装置

パネルレベルパッケージング

基板、プロセス要件、スループット、製造統合のニーズに基づいて、各種Evatec のプラットフォームから選択いただけます。 Evatecの専門家が、お客様の仕様に合わせた適切なプラットフォームを見つけるお手伝いをいたします。写真のリンクをクリックして、各プラットフォームの詳細をご覧ください。

CLUSTERLINE® 600

650x650mmまでの大面積パネルサイズに対応する、脱ガス、エッチング、成膜技術を統合したFOPLPおよび次世代IC基板処理向けの市場をリードする装置ソリューション

パネルレベルパッケージングの詳細はLAYERSをご覧ください。

より環境に優しいPCB / IC基板業界

原材料とウェットプロセスの削減、製品ビルドアップの最適化、ドライプロセスの導入によって、PCB製造におけるCO2排出量をどのように削減できるかをご覧ください。

CLUSTERLINE® 600と次世代IC基板

CLUSTERLINE® 600プラットフォームの最近の進歩は、AIや高性能コンピューティングなどの新興市場向けの高度なIC基板製造への適合性を強調しています。

ファンアウトパッケージング技術における主要課題

Samsung Electro-Mechanicsは、Samsung GALAXY Watchの製造を成功させるために、Evatecと連携してファンアウトパッケージング技術の課題を解決した事例について語ります。