在 WLP 中实现最低拥有成本

实现异构集成

- 晶圆翘曲校正的 PVD 解决方案

- SiCN 混合键合解决方案

"种子层 "工艺

- 精密保形涂层

- 高纵横比沟槽和通孔

高性能计算与人工智能

- 散热应用

- 可焊层工艺

行业领先的生产解决方案

- 200 毫米或 300 毫米脱气、蚀刻和 PVD 工艺解决方案

- 以最低的 Rc 和最高的产量实现最佳 CoO

在晶圆级封装工艺方面久经考验的专业技术

选择 Evatec 作为您在晶圆级封装工艺方面的合作伙伴,因为我们知道我们的平台和工艺已在全球领先的封装厂中得到日常使用。无论是 CLUSTERLINE® 300 的广泛配置和工艺灵活性,还是 HEXAGON 专门针对的应用,您都可以确信总有一款生产解决方案适合您。Evatec 的晶圆级平台可处理最大 300mm 的格式,具有最高的吞吐量,支持使用长寿命靶材,并配备了独特的脱气技术,可实现 WLCSP、FOWLP 和 2.5D/3D 器件所需的最佳接触电阻和层均匀性。

凸块技术(UBM)

凸块技术是在芯片、基板和印刷电路板之间建立连接的关键技术,包括在接合焊盘上形成被称为 "凸点 "的凸起金属区域。Evatec 针对各种应用和规格提供全面的凸块解决方案。我们先进的凸点工艺有多个级别,可满足不同的间距要求,从粗间距(500 微米及以上)到超细间距(小于 50 微米)。通过减小凸点尺寸和间距,同时确保高成品率,Evatec 提高了数据传输速度,最大限度地降低了功耗,满足了现代电子设备的需求。

接触电阻(Rc)是此类互连器件的主要性能指标之一。Evatec 先进的工艺系统和创新理念可提供业内最低的接触电阻,确保键合互连的最佳性能和可靠性。凭借我们的尖端技术和专业知识,我们在先进的半导体封装应用中实现了无缝连接和强大的功能。

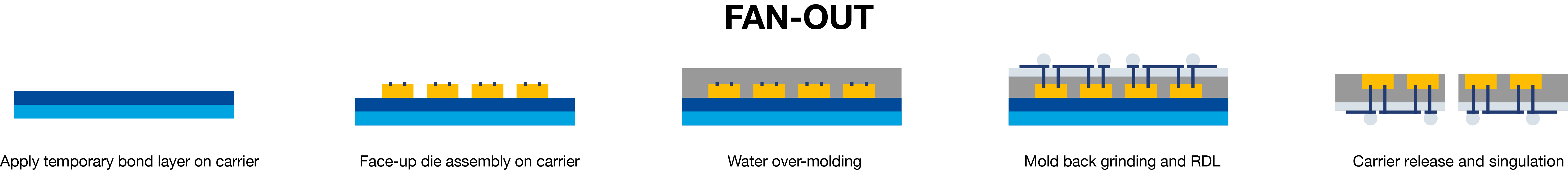

晶圆级扇出型封装(FO-WLP)

晶圆级扇出型封装(FO-WLP)的出现是为了解决传统晶圆级芯片尺寸封装(WLCSP)中芯片区域凸块空间有限的难题。采用 FO-WLP 时,器件晶圆要经过切割,然后在载体晶圆上重新定位单个裸片,使每个裸片周围有足够的空间。然后对重组晶片进行包覆成型,为再分布层(RDL)留出更多空间。

在真空设备中处理含有聚合物的基底需要特别注意,因为它们容易放气,有可能污染现有层。在 Evatec,我们的创新处理解决方案可确保高效处理,同时减少放气并将层污染降至最低,从而保证封装工艺的完整性和质量。

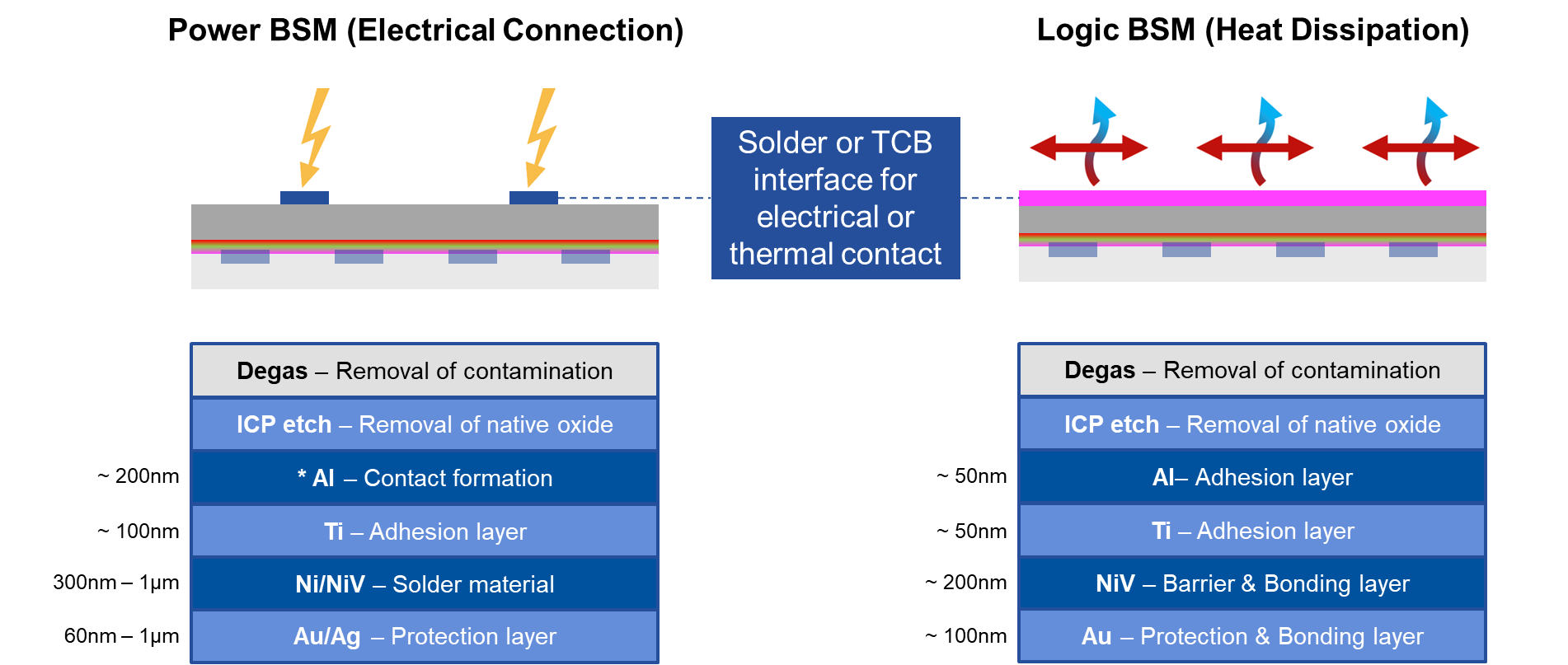

用于散热的背面金属化 (BSM)

高性能计算(HPC)在人工智能、生命科学和金融等各种应用中发挥着重要作用。为实现最佳计算能力,先进的片上系统 (SOC) 或下一代封装技术在芯片或封装层面集成了处理器、内存和存储器。然而,有效的热管理对最大限度地提高计算性能和能效构成了重大挑战。

Evatec 通过创新的薄膜沉积技术,特别是背面金属化 (BSM) 技术来应对这一挑战。我们的 BSM 解决方案有助于与冷却盖进行均匀可靠的连接,这对管理 HPC 封装产生的热量至关重要。通过在晶片背面沉积可焊层堆栈,Evatec 可确保出色的附着力、可焊性和最小的薄膜应力。这些特性对于满足严格的热要求、确保 HPC 系统的最佳性能和使用寿命至关重要。

生产设备

Evatec用于晶圆级封装的机台组合

根据您的基板、工艺要求、产量和工厂集成需求,从 Evatec 机台中进行选择。

我们的专家可帮助您找到适合您规格的平台。或者,点击按钮详细了解每个平台。

HEXAGON

专用的紧凑型大批量生产平台,适用于 200mm 和 300mm WLCSP 和 FOWLP 等晶圆级应用,提供高速加工,实现市场最低拥有成本。

CLUSTERLINE® 300

半导体行业标准 300mm 群集平台,配备专有的脱气、极冷蚀刻和金属化技术,适用于 WLCSP、FOWLP 和 TSV,提供灵活的制造能力。

在我们的《LAYERS》杂志上阅读更多有关晶圆级封装的信息

多室 PVD 系统中的交叉污染研究

HEXAGON PVD 系统是现代 WLP 应用的理想之选,可在高产量条件下提供低而稳定的接触电阻,并将腔室之间的交叉污染降至最低。

晶圆级封装中的生产率提升和最佳 Rc 控制

电子设备小型化的趋势强调了低接触电阻和稳定接触电阻的重要性,HEXAGON 的高通量 UBM / RDL 技术在 ECTC 的实验工作中得到了验证。

Chiplet 和先进封装的新时代

随着行业进入异构集成的新时代,芯片组形式的高级封装正变得越来越重要。什么是芯片组,有哪些优势?