帮助客户在新架构中创新

实现三维集成

- 应力管理和晶圆翘曲校正

- 为混合键合定制的 PVD 工艺

保形镀膜

- 适用于需要多级互连架构的各种器件

- 适用于从 ~400-500 纳米到小于 100 纳米的大 CD

溅射硬掩膜

- 经过验证的 Evatec PVD 工艺解决方案

- 广泛的材料和工艺组合

为什么 Evatec 是您在前端领域的合作伙伴?

过去几十年来,制造更小、更快、更高效的器件的需求推动了半导体行业的发展。随着二维微缩技术的进步放缓,需要采用其他方法来提升器件性能。

为了进一步提高逻辑密度,需要新材料、新架构(例如晶体管设计)的创新或引入第三维的创新。

Evatec 溅射设备(例如用于处理 300 毫米晶圆的 CLUSTERLINE® 300)提供专用的 CMOS 配置,以提高真空度、缺陷和污染性能。

以下是我们可以为您提供支持的部分领域,如有任何疑问,请联系我们。

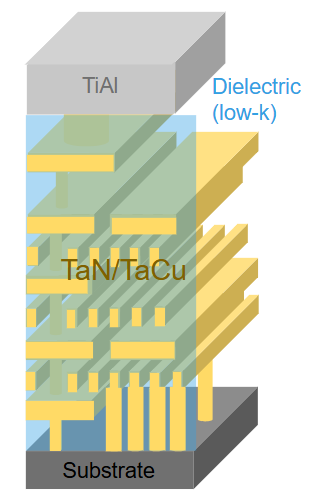

集成电路多层互连金属化

集成电路内的互连金属化可实现器件之间的信号传输。早期互连金属化通常采用铝,但后来业界采用了带有 Ta/TaN 阻挡层的铜,以满足更严格的设计规则并降低电阻率。如今,Evatec 凭借其专用的 CMOS 兼容 CLUSTERLINE® 300 系统,可满足传统和先进的金属化需求。

我们灵活的硬件配置,包括通过冷热静电吸盘 (ESC) 实现的先进温控,确保了工艺的高重复性。我们提供钛铝工艺解决方案,用于高带宽存储器 (HBM) 等应用中更高层次的金属化和金属焊盘形成。此外,我们的工艺团队随时准备支持您开发 Ta/TaN 阻挡层和 Cu 种子层工艺,以满足下一代互连的需求。

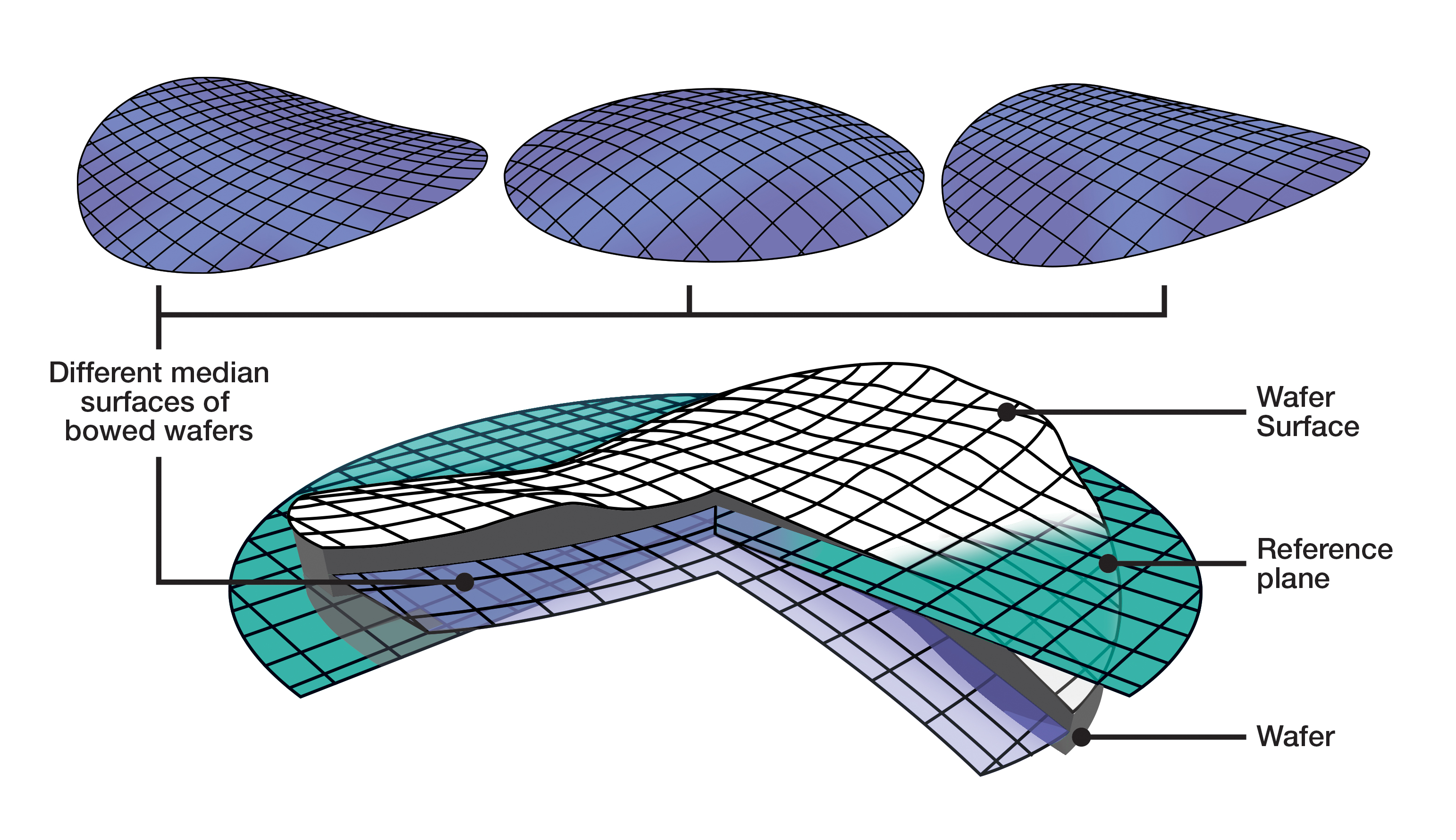

翘曲补偿

半导体制造中的翘曲补偿

随着半导体器件日益复杂,为了实现更高的功能和存储密度,垂直堆叠晶圆的应用日益广泛。克服由此产生的晶圆变形和衬底翘曲的一种方法是通过介电PVD层进行背面晶圆翘曲校正 (WPC)。使用负向应力的氮化物PVD解决方案可以在低温下形成可调应力膜,从而保持晶圆的完整性。

成功WPC的关键参数包括应力范围、层厚度、衬底温度、边缘卷边和化学特性,尤其是在蚀刻去除等后处理步骤中。

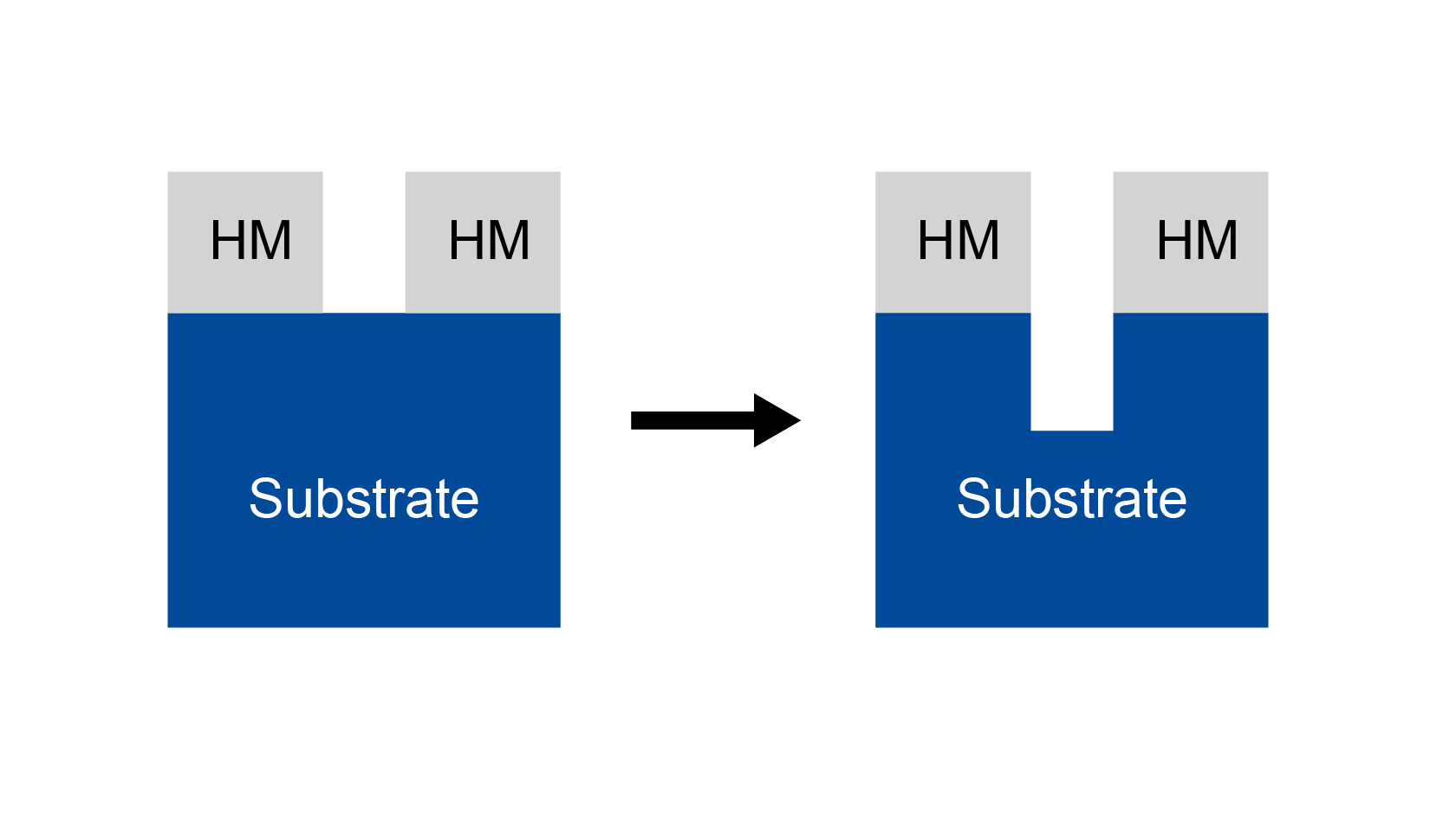

硬掩模

半导体制造中的硬掩模

硬掩模在包括存储器在内的器件制造过程中发挥着至关重要的作用。这些掩模有多种用途:

- 图案定义:硬掩模定义图案,充当蚀刻掩模或定义注入区域。它们可以精确地指导后续工艺步骤。

- 刻蚀停止层:除了图案之外,硬掩模还可以充当刻蚀停止层,以控制和限制刻蚀工艺的损耗。

- 刻蚀选择性和效率:硬掩模必须具有较高的刻蚀选择性。这一特性确保在等离子刻蚀过程中,掩模材料保持完整,同时选择性地去除底层。这使得能够使用更薄的厚度并提高工艺产量。

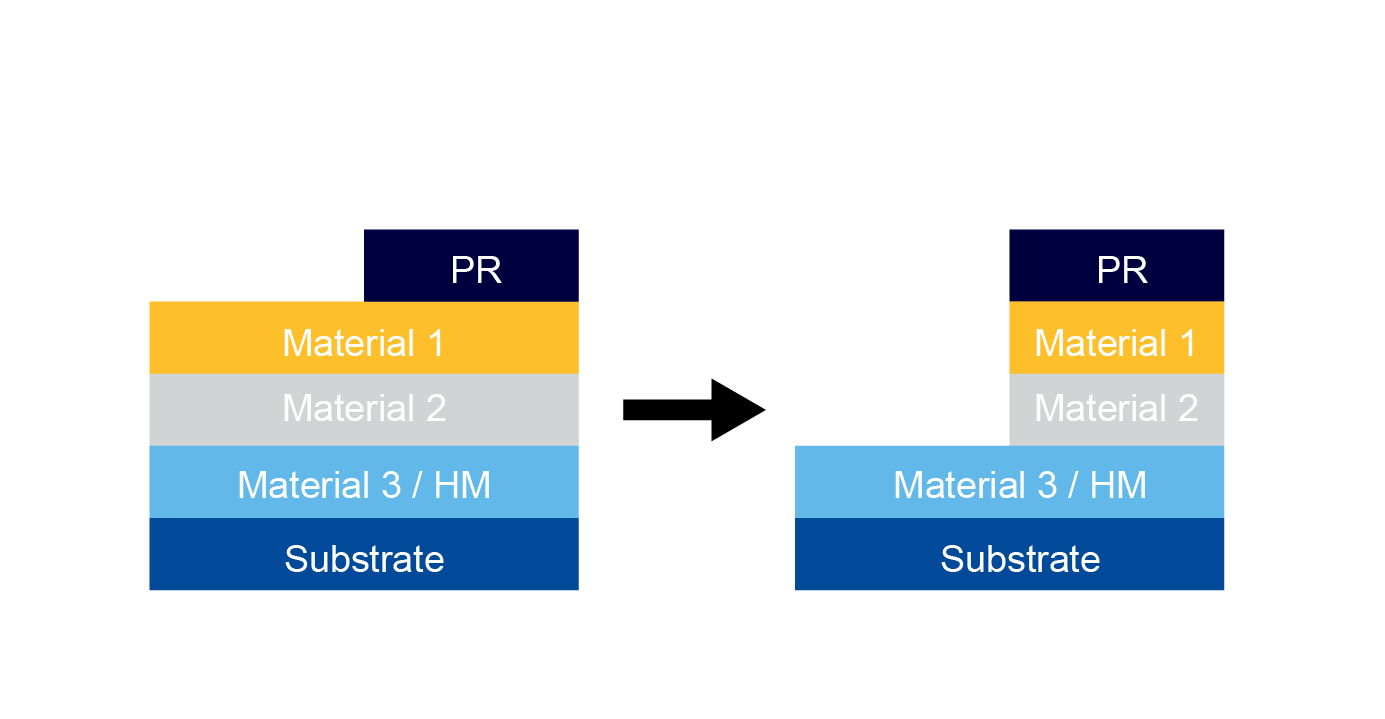

然而,要获得有效的硬掩模,还需要考虑其他因素:

- check 机械性能:硬掩模应能够承受制造过程中的各种应力,以确保其稳定性和耐用性。

- check 沉积技术:化学气相沉积 (CVD) 因其均匀且保形的覆盖范围而被广泛用于硬掩模沉积。然而,在热预算严格或必须控制高氢含量的应用中,它可能面临局限性。在这种情况下,物理气相沉积 (PVD) 是一种可行的替代方案。

- check 材料选择:多种成分可供选择,例如 MoO2、SiC(N)、Ta2O5 和 SiN。每种材料均可证明其在特定应用中的适用性。

如需了解更多信息或有任何疑问,请随时联系我们

生产设备

Evatec 前端机台组合

根据您的基板、工艺要求、产量和工厂集成需求,从 Evatec 的平台中进行选择。

我们的专家随时准备协助您找到符合您规格的合适平台。或者,点击按钮详细了解每个平台。

CLUSTERLINE® 300

12 英寸晶圆盒到盒式集群式设备符合半导体行业传输和跟踪标准,适用于单片工艺模块内的单晶圆处理,可实现晶圆级光学等应用的精度。

在我们的《LAYERS》杂志上阅读有关前端的更多信息

超越摩尔定律

芯片制造商面临三维集成电路和异构集成的挑战,需要管理热预算和晶圆平面度。Evatec 为先进的 CMOS 晶圆厂提供解决方案。