お客様の新しい構造革新を支援

3Dインテグレーションの実現

- 応力管理とウェーハ反り補正

- ハイブリッド接合のためのPVDプロセス

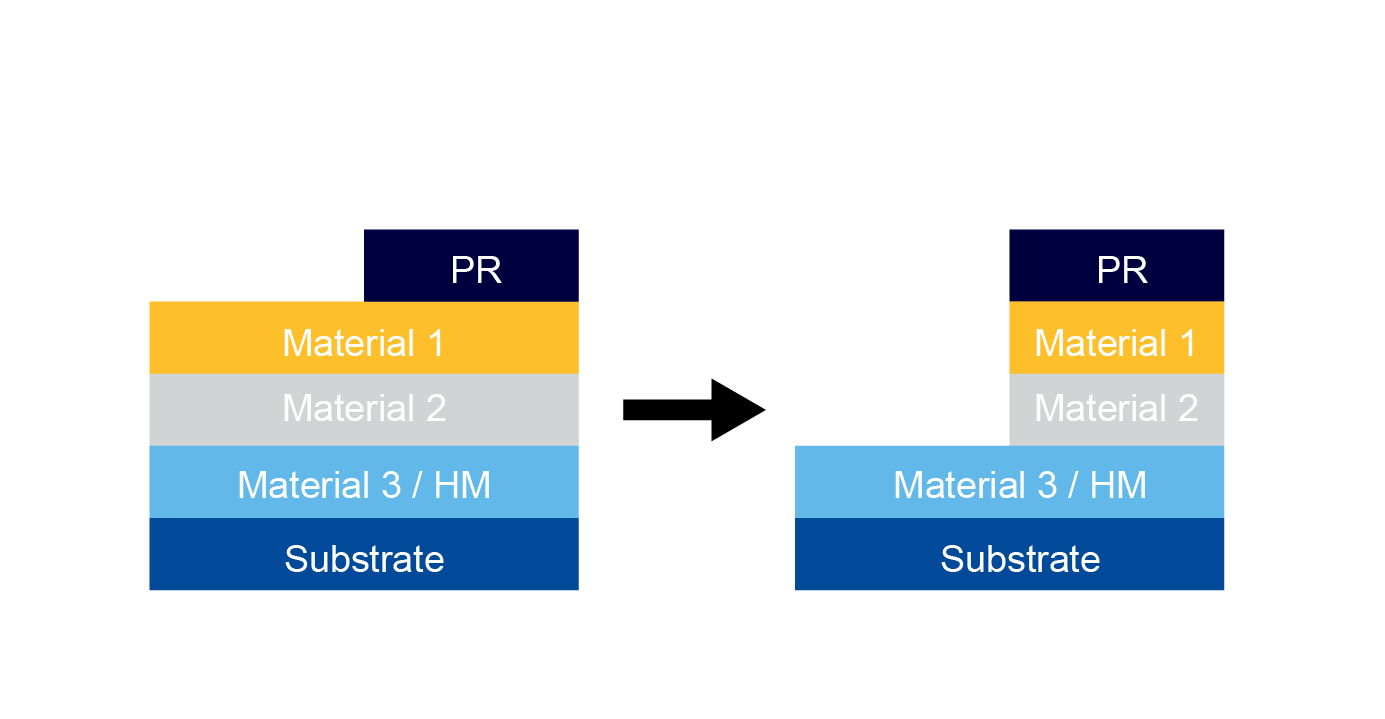

コンフォーマルコーティング

- 多層配線アーキテクチャを必要とする様々なデバイス向け

- 400~500nm程度の大きなCDから100nm未満まで対応

スパッタリングハードマスク

- 実績のあるEvatec PVDプロセスソリューション

- 幅広い材料とプロセスのポートフォリオ

エバテックがフロントエンドのパートナーである理由

より小さく、より速く、より効率的なデバイスを作るという要求は、過去数十年にわたって半導体産業を牽引してきた。2Dスケーリングの進歩が鈍化するにつれて、デバイスの性能を高めるための他のアプローチが必要とされています。

ロジック密度をさらに高めるには、新しい材料やアーキテクチャ(トランジスタ設計など)の革新、あるいは3次元導入による革新が必要です。

300mmウェーハ処理用のCLUSTERLINE® 300のようなエバテックのスパッタ装置は、真空、欠陥、コンタミネーション性能を改善したCMOS専用構成でご利用いただけます。

ここでは、私たちがサポートできる分野の一部をご紹介します。

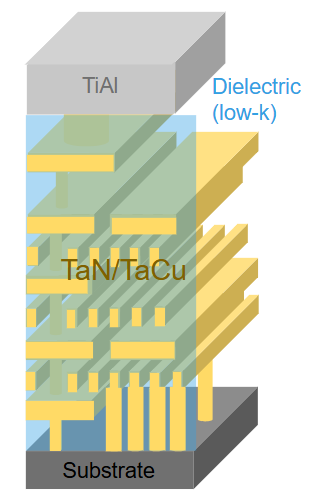

IC用マルチレベル配線メタライゼーション

集積回路内の相互接続メタライゼーションは、デバイス間の信号伝達を可能にします。初期の世代ではアルミニウムが一般的でしたが、その後、厳しい設計ルールに対応し、抵抗率を低減するために、Ta/TaNバリア層を持つ銅が採用されました。現在、エバテックでは、CMOS対応のCLUSTERLINE® 300システムにより、従来のメタライゼーションと高度なメタライゼーションの両方のニーズに対応しています。

冷間および熱間静電チャック(ESC)による高度な温度制御を含む当社の柔軟なハードウェア構成は、高いプロセス再現性を保証します。当社は、高帯域幅メモリ(HBM)などのアプリケーションにおいて、より高度なメタライゼーションやメタルパッド形成のためのチタンアルミプロセスソリューションを提供しています。さらに、当社のプロセスチームは、次世代相互接続の要求を満たすTa/TaNバリアおよびCuシードプロセスの開発をサポートする準備が整っています。

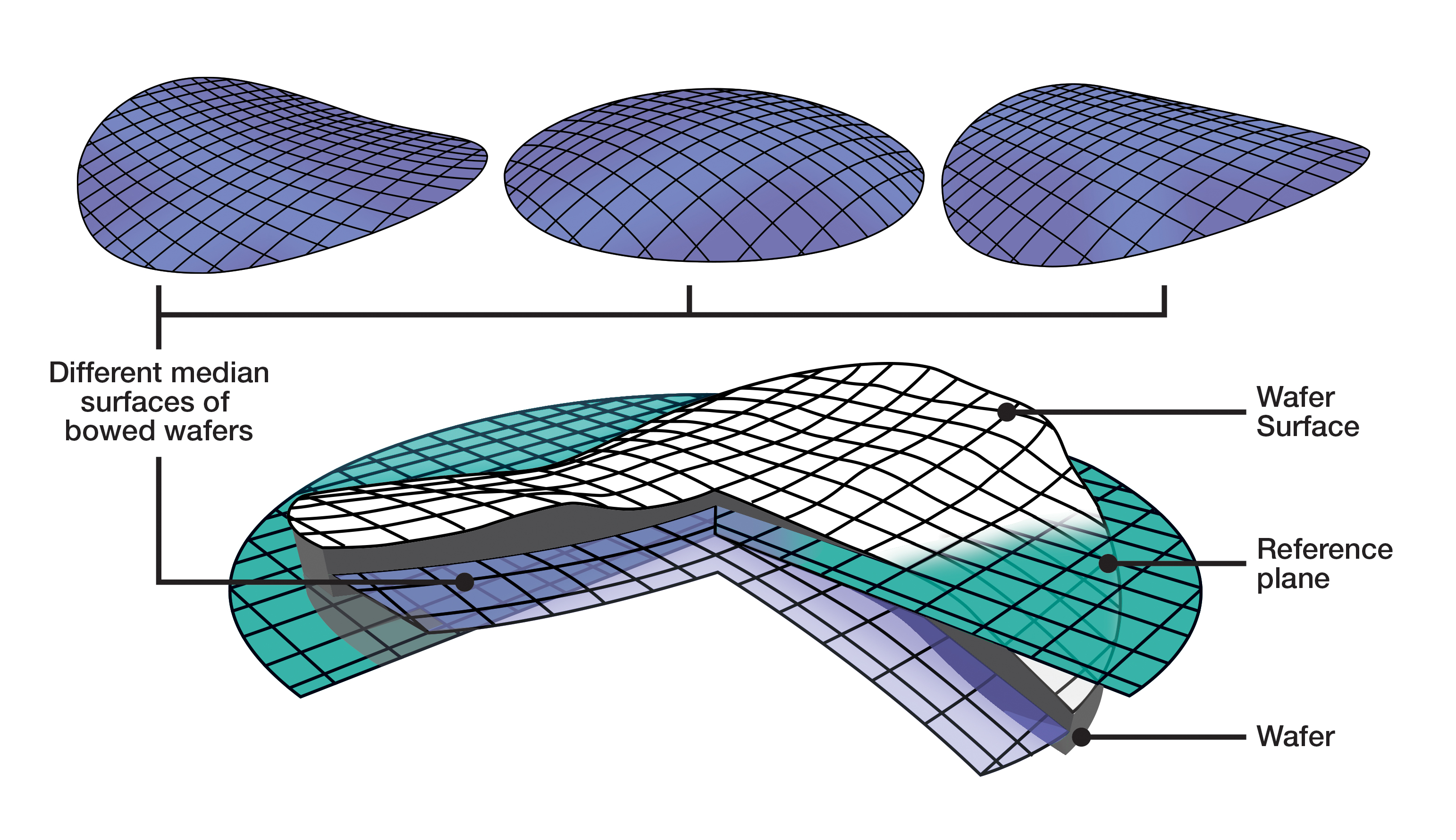

ワーページコンペンセーション

半導体製造における反りへの対応

半導体デバイスの複雑化に伴い、より高い機能密度と記憶密度を実現するために、ウェハを垂直方向に積層することがますます増えています。その結果生じるウェーハの変形や基板の反りを克服する方法のひとつが、誘電体 PVD 層による裏面ウェーハ反り矯正(WPC)です。圧縮窒化物PVDソリューションを使用することで、低温で応力膜を調整することができ、ウェハの完全性を保つことができます。

WPCを成功させるための主な仕様には、応力範囲、層厚、基板温度、エッジロールオフ、化学的特性、特にエッチング除去などの後処理工程が含まれています。

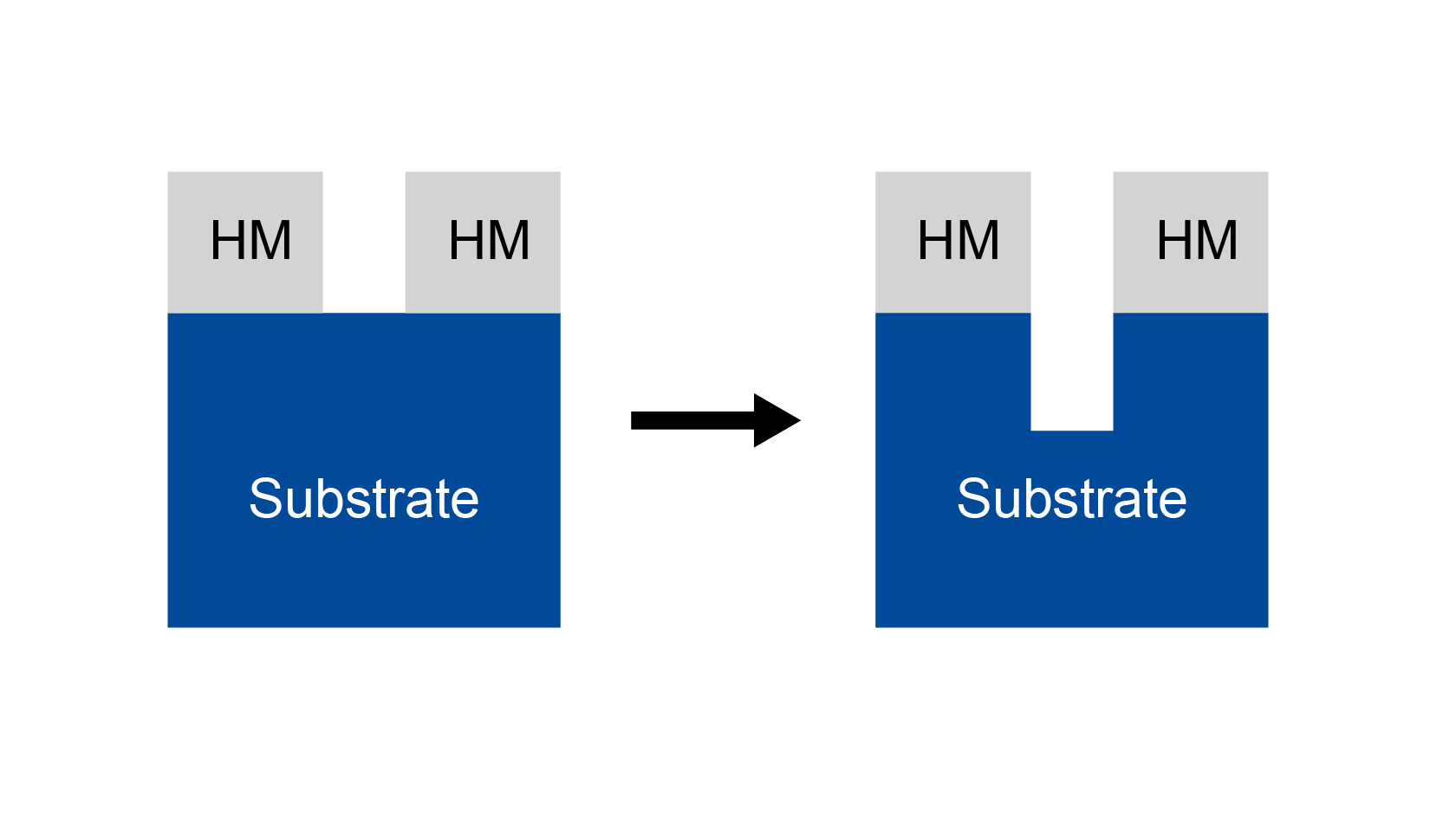

ハードマスク

半導体製造におけるハードマスク

ハードマスクは、メモリを含むデバイスの製造プロセスにおいて重要な役割を果たしています。これらのマスクには複数の目的があります:

- パターン定義:ハードマスクはパターンを定義し、エッチマスクとして、または注入領域を定義します。後続の加工工程を正確にガイドします。

- エッチストップ: パターンに加えて、ハードマスクは、エッチプロセスの負債を制御し制限するためのエッチストップとしても機能します。

- エッチング選択性と効率:ハードマスクには高いエッチング選択性が求められます。この特性により、プラズマエッチング中、マスク材料は無傷のまま、下層が選択的に除去されます。これにより、より薄い層の使用と高いプロセススループットが可能になります。

しかし、効果的なハードマスクを実現するには、さらなる要素を考慮する必要があります:

- check 機械的特性:ハードマスクは、製造時のさまざまな応力に耐え、安定性と耐久性を確保する必要があります。

- check 蒸着技術:化学気相成長法(CVD)は、均一でコンフォーマルに成膜できるため、ハードマスク成膜に広く使用されています。しかし、厳しい熱バジェットが要求されるアプリケーションや、高い水素含有量を管理しなければならないアプリケーションでは、CVDには限界があります。このような場合、物理的気相成長法(PVD)が有効な代替手段となります。

- check 材料オプション:MoO2、SiC(N)、Ta2O5、SiNなど、さまざまな組成をご用意しています。各材料は、特定の用途に適していることを実証できます。

詳細やお問い合わせは、お気軽にご連絡ください。

量産向け装置

フロントエンドのためのエバテックツールポートフォリオ

お客様の基板、プロセス要件、スループット、工場統合のニーズに応じて、エバテックのプラットフォームからお選びください。

当社の専門家が、お客様の仕様に合わせた適切なプラットフォームを見つけるお手伝いをいたします。または、ボタンをクリックして各プラットフォームの詳細をご覧ください。

CLUSTERLINE® 300

カセットツーカセット方式の 12 インチ クラスターは、ウェーハ レベルの光学系などのアプリケーションでの精度を実現する単一プロセス モジュール内での単一ウェーハ処理に関する半導体業界の処理および追跡標準に準拠しています。

フロントエンドの詳細についてはLAYERSをご覧ください。

ムーアの法則を超えて

チップメーカーは3D ICやヘテロジニアスインテグレーションにおいて、熱バジェットとウェーハ平坦性の管理という課題に直面しています。Evatecは、先進的なCMOSファブ向けのソリューションを提供しています