# LAY ERS

# SEMICONDUCTOR & ADVANCED PACKAGING

From 310x310 mm panel processing to innovation in SiC Power on 6 & 8 inch

# COMPOUND & PHOTONICS

Process developments for PZT & Micro LED and leveraging nanolaminates for OICs

LAYERS magazine is produced by Evatec AG, Hauptstrasse 1a, CH-9477 Trübbach, Switzerland. All information is correct to the best of our knowledge at the time of going to press. Product descriptions, photos and data are supplied within the brochure for general information only and may be superseded by any data contained within Evatec quotations, manuals or specifications. Evatec AG cannot be held responsible for any errors or omissions.

Electronic distribution from November 2025. Printed distribution from December 2025.

For any comments or queries contact allan.jaunzens@evatecnet.com. ©2025 Evatec AG. Editor-in-Chief: Allan Jaunzens. Editors: Beatrice Eichmueller & Anna Bicker Design: Darren Stacey / Doubletake Design Ltd. (UK). Photography: Peter Fuchs / www.fuchs-peter.ch

| CEO | MILL | COME  |

|-----|------|-------|

| CEU | WEL  | .COME |

| Staying close in changing times                                                         | 4   |

|-----------------------------------------------------------------------------------------|-----|

| CORPORATE                                                                               |     |

| Strategy in action                                                                      | 8   |

| From handover to high performance                                                       | 12  |

| Stefan Marxer, COO: A new chapter in operations                                         | 16  |

| Going big in Japan                                                                      | 18  |

| TECHNOLOGY HOTSPOT                                                                      |     |

| Keeping cool with the hottest technology                                                | 22  |

| PEALD: The smartest plasma, the purest films                                            | 26  |

| Innovations and opportunities in Panel Level Packaging                                  | 32  |

| Welcome to Advanced Directional Sputtering (ADS)                                        | 34  |

|                                                                                         |     |

| FRONTEND                                                                                |     |

| 300mm frontend integration                                                              | 40  |

| ADVANCED PACKAGING                                                                      |     |

| Welcome to small panel processing – up to 310x310 mm!                                   | 44  |

| Development of a highly sensitive test vehicle                                          | 48  |

|                                                                                         |     |

| POWER DEVICES                                                                           |     |

| Enabling robust SiC power device fabrication with amorphous-carbon sputtering           | 54  |

| SOLARIS® – Increasing throughput for thick aluminum layers in power device applications | 58  |

| Powering the SiC future                                                                 | 62  |

| MEMS                                                                                    |     |

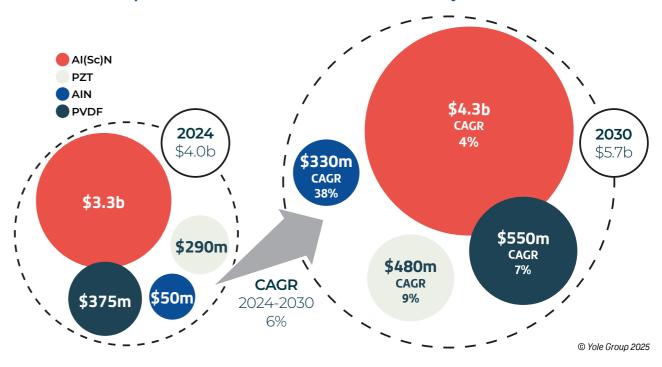

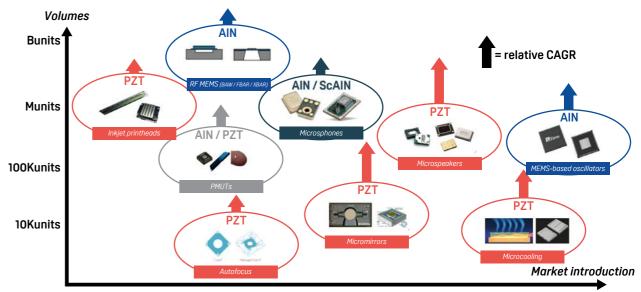

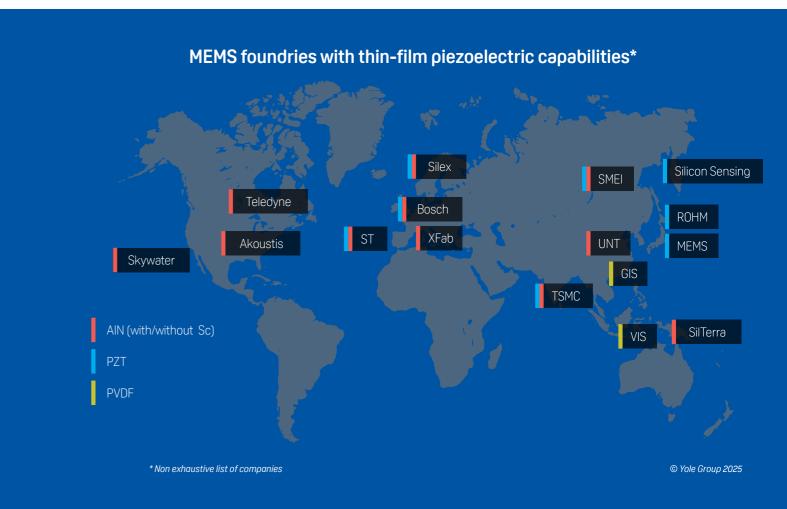

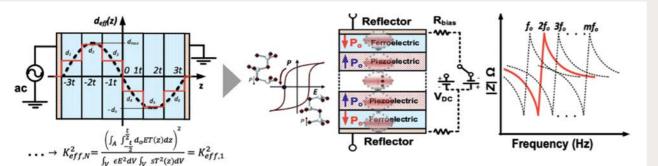

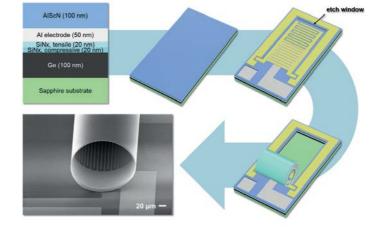

| The rise of piezoMEMS                                                                   | 70  |

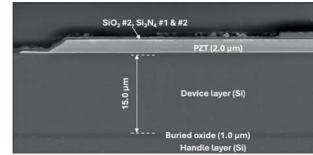

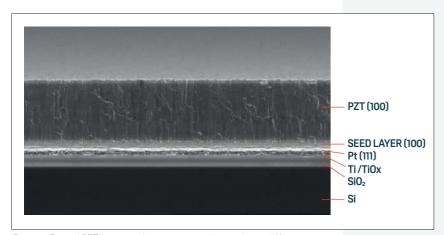

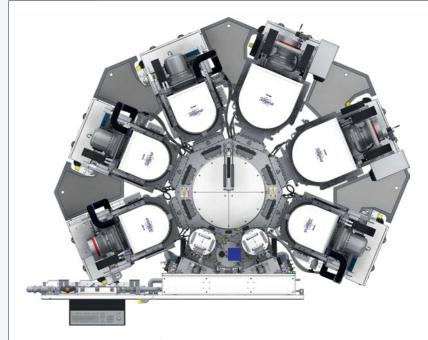

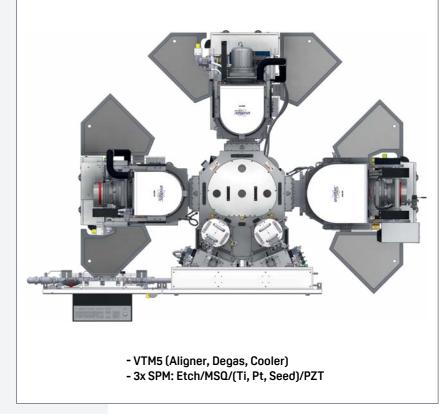

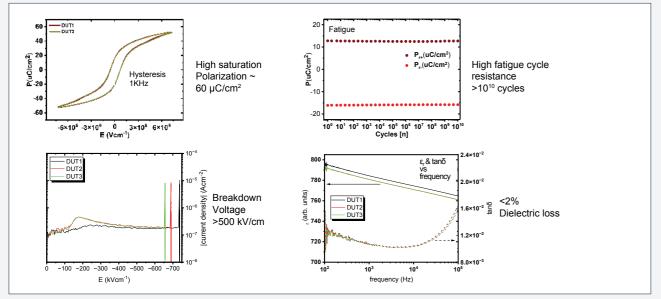

| PZT a long history with an exciting future                                              | 74  |

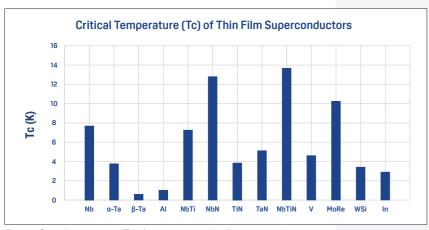

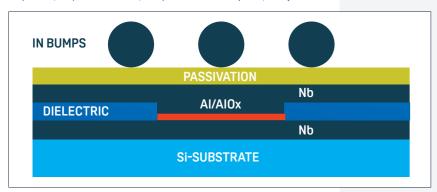

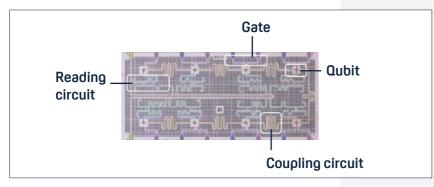

| Superconducting thin films for Quantum Computing                                        | 80  |

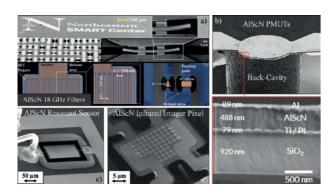

| Flying the high performance piezoelectrics flag in the USA                              | 88  |

| MIDELECC                                                                                |     |

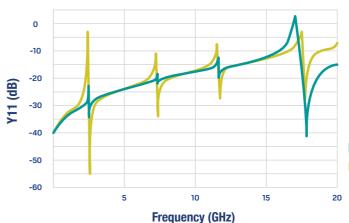

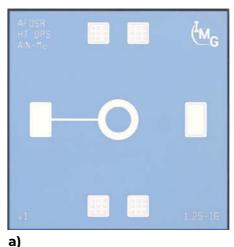

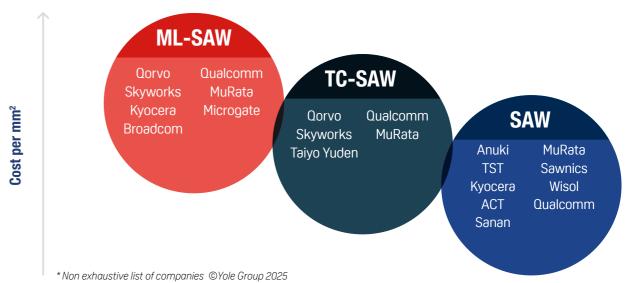

| WIRELESS RF filters in 2025                                                             | 94  |

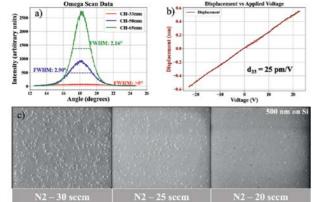

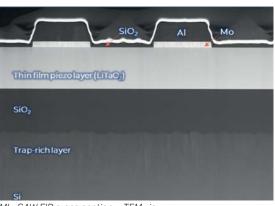

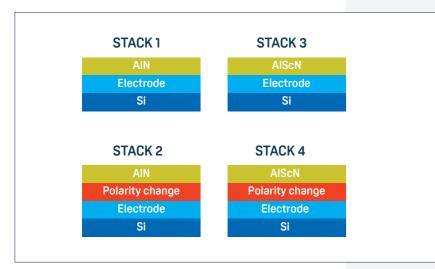

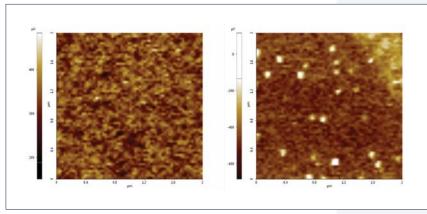

| Polarization control of AlScN piezoelectric films in high-volume production             | 96  |

|                                                                                         |     |

| OPTOELECTRONICS                                                                         |     |

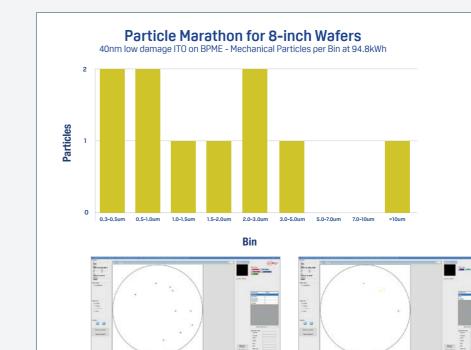

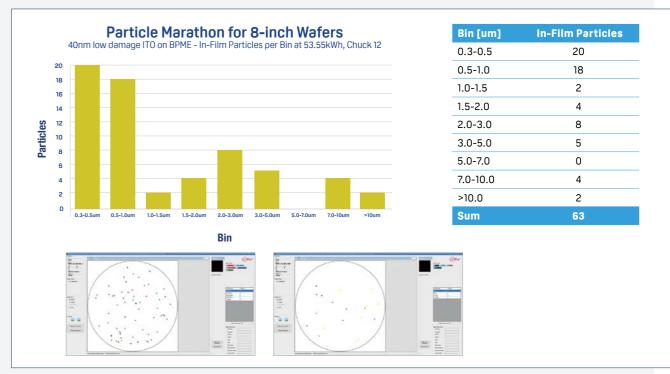

| It's all about particle control                                                         | 100 |

| Evatec LED know-how enabling an exciting EV future                                      | 104 |

| PHOTONICS                                                                               |     |

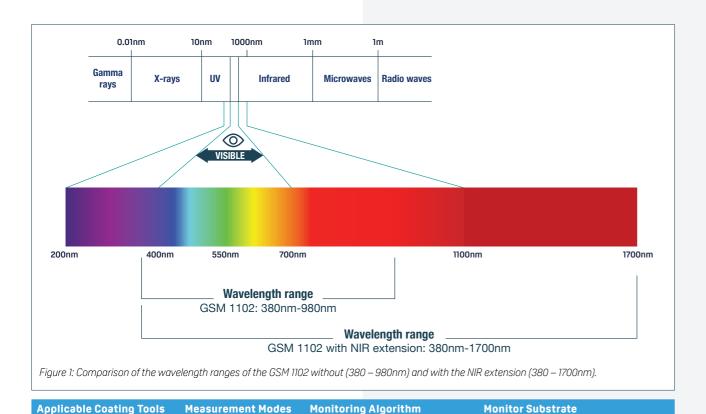

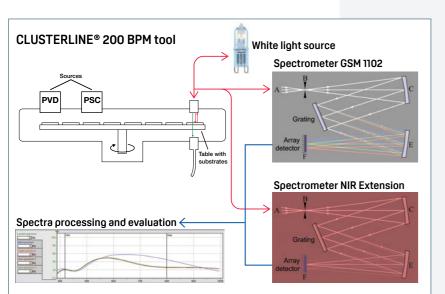

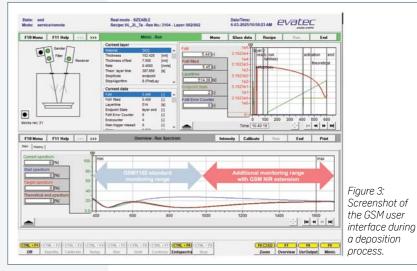

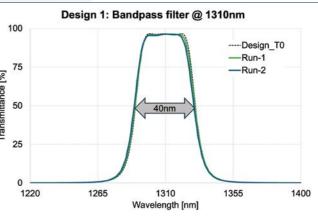

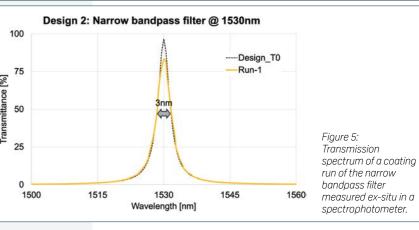

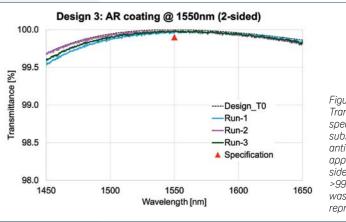

| Optical monitoring now with even "broader shoulders"                                    | 106 |

| Quantized Nanolaminates                                                                 | 110 |

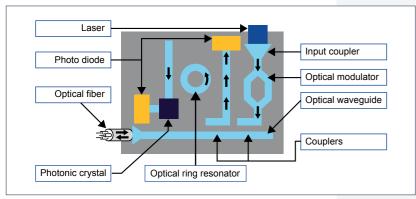

| Photonic integration in the AI era                                                      | 118 |

| ME ADE HEDE FOR YOU                                                                     |     |

| WE ARE HERE FOR YOU Worldwide Evatec contacts                                           | 122 |

| MOLIOMING ENGLEY COLLIGGES                                                              | 122 |

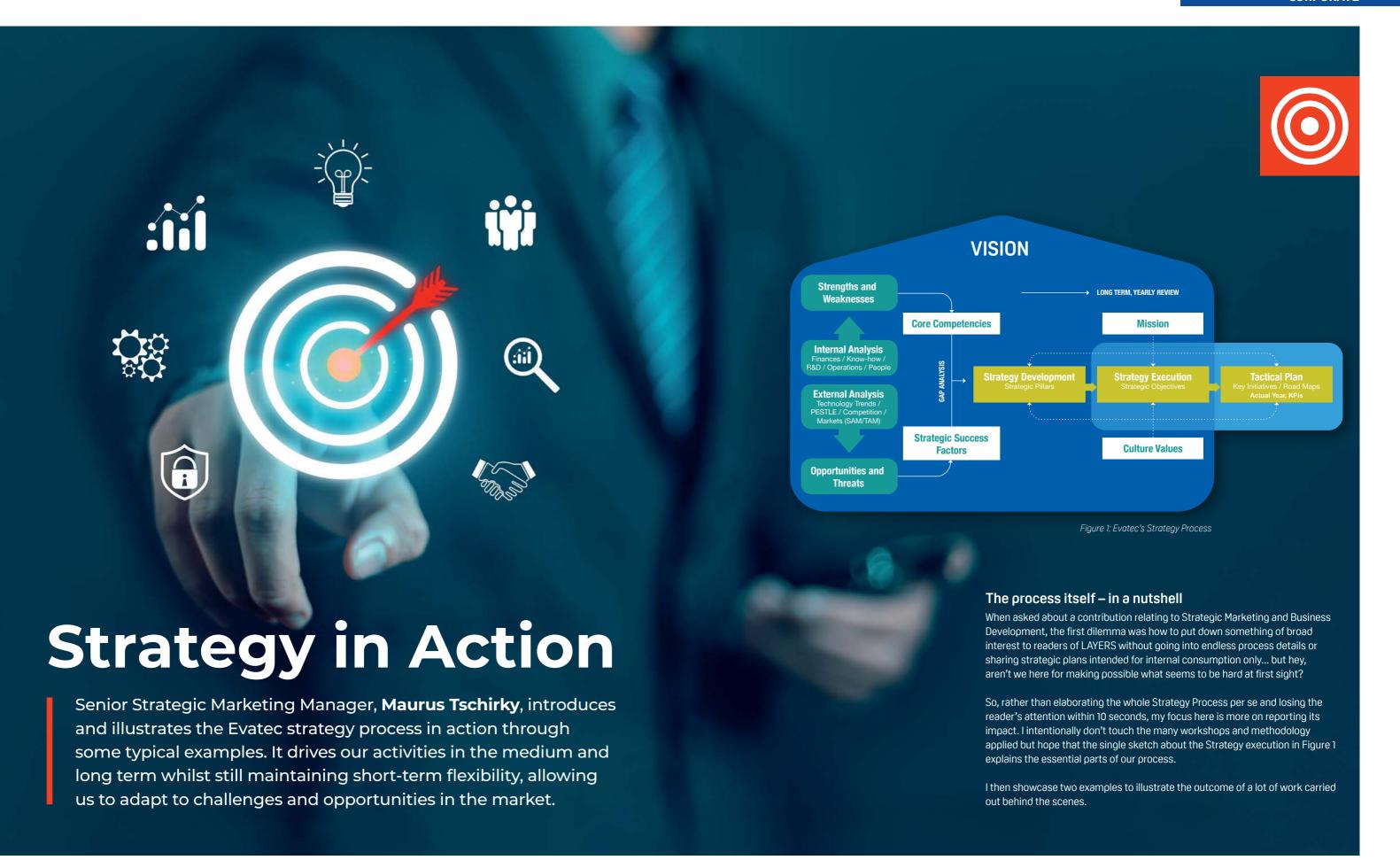

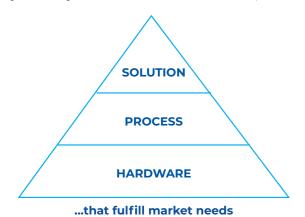

It starts with the company vision. Then as in any strategy process, there follows a thorough analysis of the status quo both internally and externally. The outcome generally answers the questions about what we ARE able to do in comparison to what we NEED to be able to do. The identified gaps represent the playing field for the Strategy Development.

The general directions are defined here, with the clear purpose of serving as guidelines for the detailed items within the Tactical Plan. Any activity therein must follow the general direction and contribute to the overall goals. We are aiming to create an environment that is agile and flexible to adapt to the market's needs. "Strategic Marketing and Business Development" very much go together.

While the internal analysis is often rather straight forward, the external factors appear ever more complex

- most prominently represented by the currently unpredictable and erratic geo-political turmoil. Make no mistake, the SEMI Industry is probably the most globalized eco-system you can find. Without global contribution, participation and free trade, this industry would not be where it is today.

At the same time, the market creates certain positions of strength and power, clearly resulting in dependencies. The widespread use of thin film technology gives rise to a heightened awareness of the strategic opportunities of being able to tap into the supply of semiconductor devices. However, localization, various 'Chip Acts', countless regulations and restrictions might even pave the way for the establishment of competing spheres.

The situation is consequently very complex, and things can also happen outside our range of influence, with either detrimental or beneficial effects.

Continuously assessing the latest developments is therefore essential and that's exactly what we do in regular reviews. What therefore might come across as straight forward and utterly logical is, in fact, much more complicated than at first glance. Human factors and company culture both have a huge influence on the outcome of this highly dynamic process which takes place under the umbrella of the company vision, values and management principles.

Our process recognizes both the need to remain agile for the short-term, whilst being persistent on activities for the mid- and long-term. The big picture lasts longer and enables major developments and programmes over several years, whereas the Tactical Plan defines the Initiatives and KPIs for the actual year. But let's leave the theory behind and introduce two real examples of our Strategy Execution:

| Market Segments | MEMS                                                   | Wireless                                                     | Power          | WLO                                     |

|-----------------|--------------------------------------------------------|--------------------------------------------------------------|----------------|-----------------------------------------|

| Materials       | AIN, AIScN, PZT, KNN                                   | AIN, AIScN, SiGe, LiNbO <sub>3</sub> , (LiTaO <sub>3</sub> ) | GaN            | LiNbO <sub>3</sub> , BaTiO <sub>3</sub> |

| Properties      | Highest crystallinity, quasi-epitaxy for all materials |                                                              |                |                                         |

| Seeding         | t.b.d.                                                 | t.b.d.                                                       | Hot AIN buffer | SrTiO₃ for BTO                          |

| Material Class    | 'Functional Ceramics' (Wurtzites, Perovskites,) |

|-------------------|-------------------------------------------------|

| Hardware Features | Temperature, Low Energy Impact, Seeding         |

Figure 2: Evatec breakdown of requirements, hardware and processes

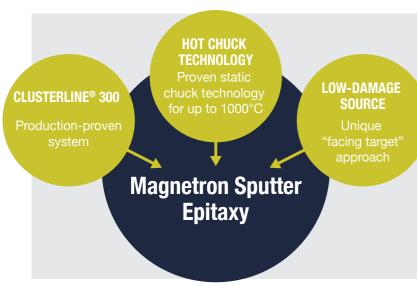

### 1. An EPIC\* story out of the Internal Analysis

We start with an important activity that has its roots in the deep-dive analysis of our core competencies – the internal analysis. A growing number of requests and needs from various market segments appeared to reveal certain similarities. From Gallium Nitride (GaN) in Optoelectronics and Power Devices, to Lithium Niobate (LNO) and Aluminium (Scandium) Nitride (Al(Sc)N) for Wireless and Photonics, Barium Titanate (BTO) for Photonics, we recognized the general need for highest crystallinity of a somehow related class of materials (Figure 2).

Luckily, we have dealt with some of those materials for two decades already. Piezoelectric effects have been at the

heart of our success in MEMS and Wireless applications over years, with ferroelectricity now opening new applications and electrooptic properties gaining momentum due to the growing importance of Photonics in the industry. These properties and characteristics, often called multiferroics, are at the very heart of functional materials with regards to transducing one physical quantity into another one.

Many of those materials require particular hardware and process control features in our systems to achieve the specified properties. That's what we have been developing so far and continue to develop as part of our long-term strategy.

Footnote: EPIC is an acronym combining the words Epitaxy and Photonic Integrated Circuits.

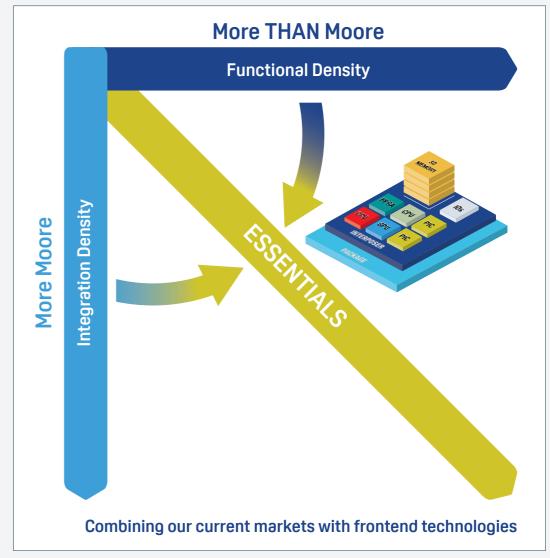

### 2. External view allows for reaching the sky in Frontend Integration

It is from constant exposure to customers and comparison with competition that we recognized the trend for ever smaller feature sizes and thus the evolution of the 3rd dimension in our customers' devices.

Apart from the very specific technology developments demanded by individual market segments, we also recognized the needs for "pure play" technology which they all might leverage if we could provide answers to capabilities including trench fillings, via coverages and liners.

An entire program for 300mm Frontend Integration (see article page 42) was therefore created to ensure Evatec remained "on the front foot" for supporting 3D-structures. This was not an application or device. It was an enabling technology that appeared across multiple markets. This program therefore has at its core the goal of providing "building blocks" and a portfolio of solutions that can be tailored to the need of individual customers.

The term 3D Heterogeneous Integration not only includes but also describes both axes contributing to what the community rightly calls the "Essentials", (Figure 3).

Figure 3: The Big Picture – Innovations for future chips.

### It's a balance

These two examples illustrate a subset of conclusions we drew out of the initial Strategy Process. Where the EPIC story comes out of an internal perspective, 300mm Frontend Integration originates in the continuous observation of the market and technology developments. We implemented these findings into our roadmaps and long-term planning whilst still remaining flexible and agile to any emerging customer needs in the shorter term.

David Dietsch, Product Marketing

Manager Customer Service, explains

how "Ramp-Up Support" helps

customers move smoothly from

installation to stable production.

With hands-on guidance and realtime expertise, this service ensures

customer personnel feel confident

and ready to unlock the full

potential of their new equipment.

# Getting started with your new equipment

Bringing a new tool into production is a critical milestone. It marks the point where planning gives way to execution. The tool has been installed, testing completed and "Final Acceptance" signed (FAT). Now, the focus turns to your team who must qualify and release processes and get the tool ready for production.

This phase can be demanding, "go live" with production must stay on schedule, qualification windows are tight, and your internal teams expect clear progress. Engineers begin working with a system they may not yet fully know. Operators need time to build confidence. Process tweaks are still ongoing. Meanwhile, your management is tracking ramp-up milestones closely.

## Why "Ramp-Up Support" matters

At this point, customers often realize that questions are still coming up. If small misalignments occur now, they tend to ripple. One overlooked setting or unclear handover process can delay qualification or affect performance. The longer it takes to stabilize the tool, the more it ties up resources and delays the moment when the tool is ready to enter production.

"Ramp-Up Support" brings the clear structures required to this critical phase. Instead of reacting to issues, an experienced engineer is already on-site to guide your team, share best practices, and help your team deliver stable tool performance faster.

# Support when it counts

Operators and maintenance staff may already have completed Level 1 and Level 2 training. They know-how to navigate the interface, operate the tool, and follow standard procedures. Still, once the tool enters active production, the environment changes. In many fabs, operators switch between platforms from different suppliers. Handling multiple workflows at once is challenging, especially during the early days of production.

Meanwhile, process engineers focus on aligning tool performance with production goals. What worked during FAT or pre-production testing may need adjusting. Parameters are often fine-tuned to match recipes, workflows, and surrounding equipment.

Even small environmental differences can affect setup. Support is often called for only after progress slows or qualification is affected. With an Evatec engineer on-site right from the start, your team receives timely guidance, clear decisions, and steady support that keeps your project on track.

### What's included

Ramp-Up Support gives you direct access to a skilled Field Service Engineer during the early phase of integration. They work closely with your team as the tool moves from installation into qualification and production.

Instead of waiting for issues to be reported and handled remotely, questions are answered in real time by an engineer who is on-site with firsthand knowledge of the issues you want to address.

Adjustments can happen on the spot if parameters need refinement. You gain clarity on how to best run the tool under your specific conditions. In short, Ramp-Up Support helps your team move faster and with more confidence.

"Start-up is always demanding, but with Ramp-Up Support it does not have to be uncertain"

### A win for both sides

Customer feedback is clear: Ramp-Up Support makes qualification smoother, and teams feel better supported during a demanding phase. Uncertainty decreases and collaboration improves. The path to production becomes more predictable.

- Fewer unexpected service calls during warranty

- Better planning and fewer delays under pressure

- Faster progress with support already in place

- Direct contact and fast answers build trust

Ramp-Up Support is more than a bridge to production. It's a chance to see what responsive service looks like in daily operations.

# Starting strong, staying strong

The first few weeks with a new tool often determine how things will progress.

Teams begin to form routines. Processes take their final shape. Expectations for performance are set. With Evatec Ramp-Up Support, the tool reaches stable performance sooner and your team gains confidence through direct, hands-on collaboration.

So why not reach out to your local Evatec contact to explore how it could support your next project.

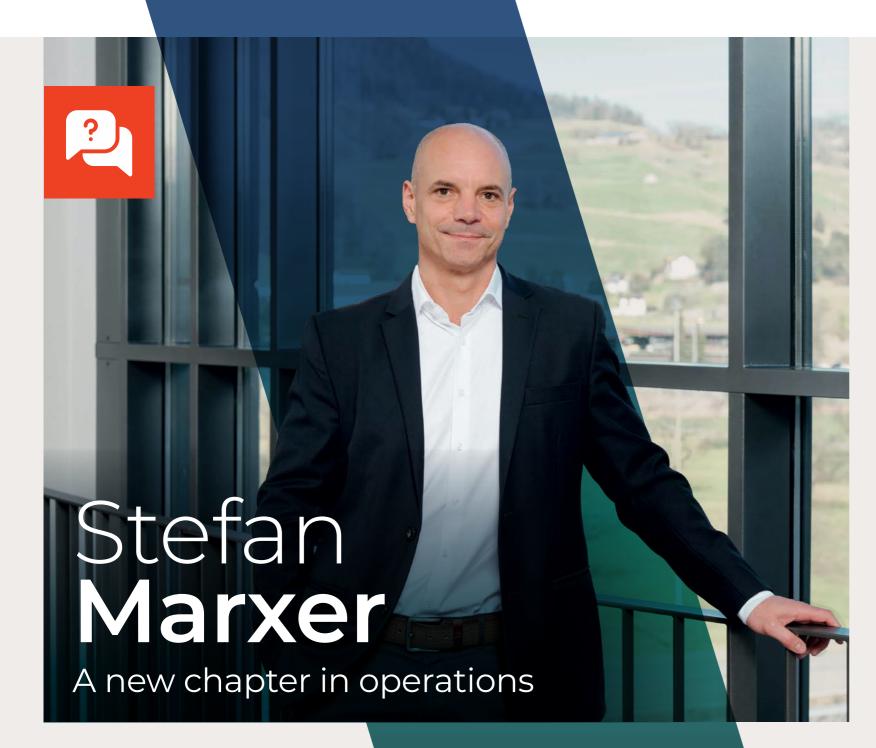

Since joining Evatec at the beginning of 2025, **Stefan Marxer** may still be "the new kid on the block" as COO, but he certainly knows a lot about our industry from the days of his apprenticeship and early career. In his interview, Stefan talks about the current challenges in Operations, how Evatec is tackling them, and what transparency and operational excellence mean in this context.

Stefan Marxer joined Evatec as Chief

Operating Officer (COO) in February

2025. Bringing more than 20 years of

international experience in operations,

including key leadership roles in Asia

and Eastern Europe, he offers extensive

industry expertise with a strong

emphasis on LEAN management and

operational excellence. Known for

his collaborative leadership style,

Stefan is dedicated to driving

process standardization and

strengthening cross-functional

teamwork.

# Can you remind us how you knew Evatec and what made you interested to join?

I began my career with an apprenticeship as a physics laboratory technician at Balzers AG in 1990 and spent a total of 16 years there, experiencing the company's transformation through Balzers, Balzers Process Systems, Unaxis, and OC Oerlikon. Since then, I've held various operational roles in international companies, including a five-year assignment in Shanghai. Most recently, I had the exciting opportunity to establish a new manufacturing site in Eastern Europe. When I learned about the position at Evatec, I immediately felt that my experience could add real value in strengthening the company's operational performance.

# What were your first impressions and how has the business changed since you left the industry back 2006?

The portfolio has grown significantly – not just in size, but also in complexity and technological sophistication. But in many ways "onboarding" felt surprisingly easy. I've reconnected with familiar faces and returned to an industry I know well, which made it feel a bit like coming home and helped me get up to speed quickly.

# What do you see as the challenges for operations from a customer perspective?

It's clear – speed, quality and cost efficiency. In rapidly changing market situations, our customers need to react quickly to help them take advantage of opportunities so speed at Evatec is essential. At the same time, quality must remain consistently high. It is a key differentiator ensuring high equipment uptime which together with cost efficiency ensures a strong value proposition through cost of ownership. However, these expectations are further complicated by geopolitical uncertainties and export restrictions, necessitating flexible, scalable solutions and adaptable supply chains.

# How do such challenges affect you internally and what are you doing to address them?

We are currently running several initiatives focused on reducing lead times, lowering manufacturing costs, and maintaining high product quality. These include simplifying internal processes and developing closer collaboration with key suppliers. We've also introduced new shopfloor management reporting to increase transparency, monitor key performance indicators (KPIs), and ensure we take immediate corrective actions when needed. A dedicated task force helps us respond quickly to supply chain disruptions and set clear priorities to ensure continuity.

# Many people talk about "Operational Excellence". What does that term mean to you?

For me, Operational Excellence means delivering consistent, efficient and reliable performance in daily operations. It focuses on optimizing procurement, inventory management, logistics, and supplier performance to reduce lead times and costs, while fostering a culture of continuous improvement. Ultimately, it's about ensuring material availability, minimizing operational costs and delivering high-quality results in a sustainable way.

# What role does transparency and data play in improving and tracking Evatec's operations processes?

Transparency is key to success. Without clear data, you can't take the right actions or measure progress. That's why we've introduced visible shopfloor boards that display KPIs and relevant information. We're also driving digitalization initiatives to track tools in assembly across the value chain and gain better insights into productivity.

# How do you see the role of Al to support you in the future?

Al is becoming increasingly important across many areas. We're currently rolling out a software solution that uses Al to support business processes like order confirmations, delivery notes, and invoices. It also helps improve the quality of master data in our ERP system. As part of this initiative, we're implementing key processes such as Purchase-to-Pay (P2P) and Order-to-Cash (O2C).

# How do you keep your team motivated and working effectively together?

It's all about being a team and pulling in the same direction. In March this year, we held a two-day workshop to define our strategy, KPIs, and the actions needed to reach our goals. This collaborative approach created strong alignment and ownership within the team. At the heart of our daily activities is the principle of working 'Effective Together', a slogan we launched to reflect our commitment to collaboration, and leadership. Regular communication, clear responsibilities, and recognition of achievements help maintain motivation and team spirit high. A big thank you to my team for the welcome and what we achieved together already!

# "The challenges are clear – speed, quality and cost efficiency"

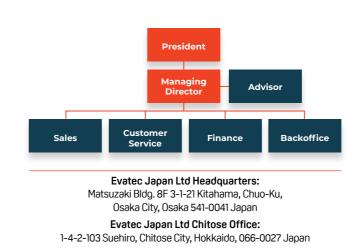

As Evatec's business in Japan continues to develop so does our organization. Evatec Japan Managing Director, **Seiji Hirai**, tells us about the recent organizational changes and how they help us deliver the local support our customers expect.

After studying materials science, **Seiji Hirai** started his career in 1998 working as a Field Application Engineer in Balzers, Unaxis, and Oerlikon. Before joining Evatec, he served as a Sales and Business Development Manager for Swedish and German manufacturers of assembly and metal processing machinery in the automotive, aerospace, and electronics sectors. He focused on expanding their business in Japan.

# Can you tell us a bit about your role as Managing Director of Evatec Japan?

My job is to use my most recent work experience managing capital equipment sales into Japan and combine it with previous know-how from the thin film industry to help Evatec now build its business further in Japan.

Since stepping into the role of Managing Director in February this year, I've taken time to understand our current position and identify opportunities for growth. Previous thin film experience in the rewritable optical disc market showed me that we could achieve a dominant position for our Swiss brand in Japan with a market share of around 90% by offering exceptional customer service and high-quality equipment. With a clear vision, stand out high quality products from Switzerland and the best local support organization for customers, I am confident we can also now grow the business of Evatec Japan too.

# Tell us about your local organization and its strengths.

We take care of everything from equipment sales, to all the daily service support our customers expect – from initial installations, to daily on-site or remote production support and upgrades.

Our order processing and finance team is there to make sure everything runs smoothly. I see it as a very flexible, agile local organization enabling us to place the right people in the right roles at the right time. Colleagues from headquarters and other global teams have not only joined daily Teams meetings but also visited customers on-site since our local Evatec Japan organization was first founded. This has helped build strong trust, the skills and motivation of our team. Looking ahead to ongoing major equipment start-ups in Japan we will use this good collaboration and teamwork to ensure successful project completions before year end. I believe Evatec's strength lies in its ability to deliver expert customer support, not only through Evatec Japan, but as a wider team in close collaboration with our Swiss headquarters and other Asian teams.

What are the challenges

Evatec faces in the

Japanese market, and

how is it different from

other markets?

In Japan, customers demand rigorous confirmation and validation of equipment specifications to ensure the production of highly reliable semiconductor products. Simply presenting strong catalog specs is not enough to secure business. Detailed discussions – known as Suriawase (alignment and adjustment) – are essential to ensure that the equipment and processes developed at our headquarters meet the exact requirements of Japanese customers. Even the reasoning behind technical decisions is closely examined.

Evatec Japan plays a key role in bridging cultural and technical gaps, facilitating smooth communication and project alignment between customers and our Swiss headquarters.

# What is Evatec Japan's main market focus?

It's an exciting time. Evatec has been working successfully through local partner Canon Marketing since 2016 developing its business for semiconductor PVD solutions. Evatec Japan was then set up in 2019 and has been focused more on starting the work building the Evatec brand in the Photonics and Advanced Packaging markets. However, as the worlds of semiconductors and photonics increasingly overlap we need to leverage synergies and know-how across different markets. It's time to put all the business activities together under one roof at Evatec Japan, effective February 2026.

For Japanese customers that brings important advantages:

- One single local Evatec organization serving all markets in Japan

- Direct communication with one team on their interests across several markets

- Easy access to the global service team

# 04

# What makes the Japanese market interesting for Evatec?

We are a good fit as Evatec can offer solutions in specialized markets where Japan has a longstanding reputation for technology leadership. The importance of quality design, manufacturing, and long product life is a shared interest in both our societies.

Evatec's approach adapting carefully to specific customer needs means we can deliver solutions where other players struggle to offer the same level of flexibility and customization.

By working closely with our customers sharing technical planning and samplings, and by tightly integrating our local efforts with the technical expertise of our headquarters, we position ourselves as a trusted consultant and solution provider in these specialized segments.

# How do you collaborate with other Evatec locations around the world?

The ongoing shortage of Service and Application Engineers is a major challenge in the semiconductor equipment industry, especially in Japan, where recruiting skilled talent is particularly difficult.

On top of that, project workloads fluctuate significantly between peak and off-peak periods. To manage this, we rely on a global support network of engineers who are trained to work seamlessly together and share a common culture. This collaboration helps us stay flexible and maintain high service quality during busy times.

# **07**

# How do you see the Japanese Market developing and what opportunities will that bring for Evatec?

We see strong growth in Advanced Packaging as a major step forward for Japan's semiconductor industry and a key opportunity for Evatec. Once overshadowed by wafer processing, the role played by packaging in enabling new technologies and devices to be manufactured cost effectively is growing. New chiplet architectures, new materials, and innovative methods are creating fresh demand for advanced deposition solutions. Evatec aims to support this shift by offering wafer and panel level technologies tailored for OSATs in Japan.

In parallel, the rise of AI semiconductors is driving demand for improved Power Devices, whilst the potential growth of application areas like Augmented Reality will drive the need for enhanced Optoelectronics. With our expertise in controlling both electrical and optical performance of thin films, our capabilities to manage heat dissipation & stress control within substrates, and our thin film know-how supporting build of 3D structures we believe Evatec is well positioned to support all these emerging needs.

# "It's an exciting time – our business in Japan is growing strongly"

# What are you most excited about for the future of Evatec Japan?

What excites me most is the strength and long experience of Evatec's global management and development teams. Many talented colleagues I worked with at Oerlikon Systems before 2008 have since been reunited at Evatec, and meeting them all again when I started was truly inspiring. I believe that a capable and well-aligned team, not just with knowledge and technology, but with a shared vision, can create real value.

Our goal is to build a "Dream Team" in Japan that not only promotes our advanced technologies and equipment, but also strengthens the Evatec brand and expands our presence in the Japanese market.

# Keeping cool with the hottest technology

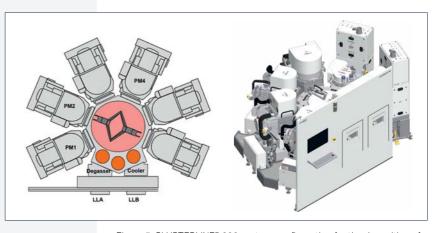

# PVD epitaxial growth on CLUSTERLINE® 300

While MBE offers excellent results in crystalline film quality, its low deposition rates limit its suitability for high-volume applications, but now it looks like we have a solution. Evatec Project Manager, Markus Mueller, tells us the story of what's been achieved so far and what's to come.

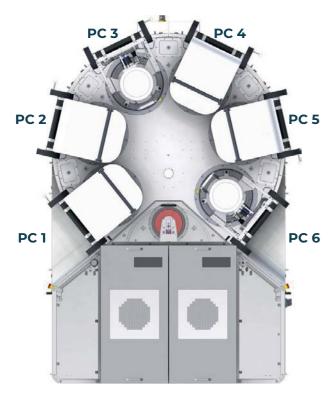

Figure 1: First demonstrator equipped with 4 FTC sources in the Evatec Competence Laboratory

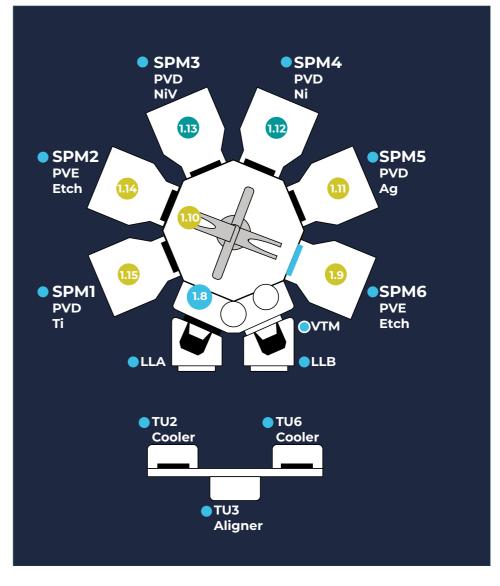

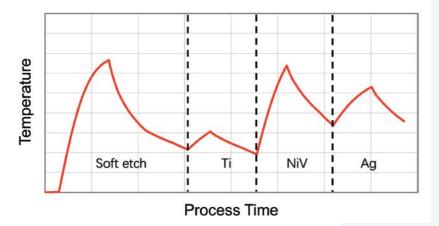

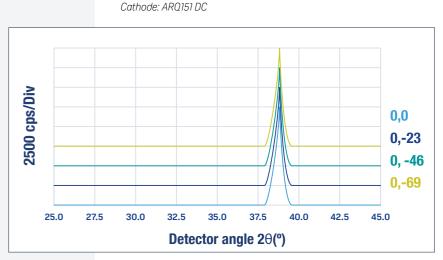

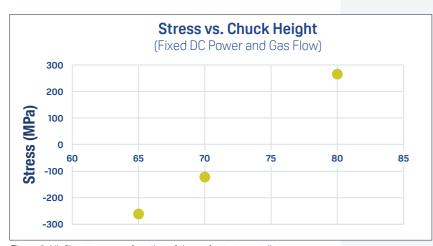

# Understanding the challenge New Evatec developments in "hot chuck" and "cathode" technology look set to enable epitaxial and quasi-epitaxial growth using PVD-based processes, delivering practical production solutions for a wide range of advanced functional materials, including BTO (Barium Titanate), GaN (Gallium Nitride), ITO (Indium Tin Oxide), and LNO (Lithium Niobate). The first thing we had to do was sit down with customers and set clear goals. Depositing crystalline films with high uniformity was a prerequisite, but we also needed to understand more about the typical materials and film thicknesses they would need in future, the acceptable levels of contamination, the throughput requirements, and other possible limitations we needed to overcome to make a PVD based solution an attractive one for the future. Figure 2 illustrates some typical process requirements. Beyond film uniformity, the system had to be designed to fulfill additional frontend fab specifications. Substrate Temperature: Up to 750°C Rocking Curve: < 0.6° (FWHM) Film thickness uniformity: < 3% (1 sigma) **Deposition rates:** > 40nm/h Figure 2: Four process challenges

osition flux [#/m2/s] at z = 97mm, em. flat, x-sec corrected

### CLUSTERLINE® 300 as the basis

The production-proven fab compatible CLUSTERLINE® 300 platform was our starting point. Our approach was to develop a modular PVD solution achieving crystalline growth by combining elevated substrate temperatures with low-damage deposition techniques. A key philosophy was to build on existing know-how wherever possible, further developing and optimizing existing production-proven component parts to shorten development times and minimize risk.

### **Very Hot Chuck Technology**

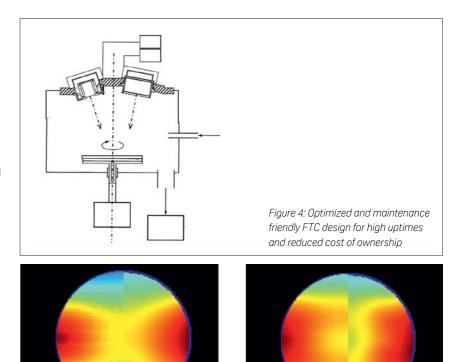

The central element was the very hot rotating chuck where Evatec built up lots of know-how over the last few years, especially when it comes to contamination reduced designs based on SiC heater elements. The newly designed chuck (Figure 3) heats 12" wafers up to 750°C with a temperature uniformity of ±2% to support crystalline growth processes. Working in combination with the modified Facing Target Cathode (FTC) source (see Figure 4), it also rotates during deposition to ensure the dynamic averaging required to meet strict film performance targets for layer properties across the substrate. Meeting these combined requirements takes precise coordination of thermal control, mechanical design, plasma optimization, and particle control, all integral parts of the overall system concept.

Handling high process temperatures in a vacuum chamber presents several challenges. Many peripheral components, such as feedthroughs, sensors, or the sources are limited to maximum temperatures. To stay within these boundaries, the development team combined:

- Thermal shielding and clever layout

- Active and passive cooling concepts

- The use of temperature-resistant materials

Since radiation is the dominant heat transfer mechanism in ultra-high vacuum, material selection for emissivity and thermal stability is a key part of the design. A dual-zone heater is used to ensure uniform temperature control across the wafer, while the cooling strategy is carefully balanced to prevent localized cold spots near the substrate.

# Facing Target Cathode (FTC) Technology

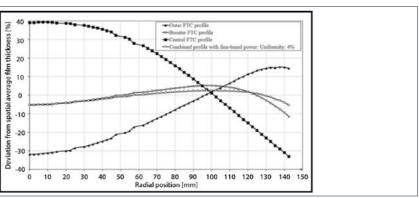

The deposition source is based on Evatec's established Facing Target Cathode (FTC) technology. The new updated design integrates four independently controlled FTC sources (eight targets total), arranged and tuned using extensive plasma simulations. This setup allows optimization of both thickness uniformity and deposition rate. Additionally, new RF and DC generators, combined with customized matching units and gas control, are being used to fine-tune process conditions.

Working at high temperatures up to 1,200°C at certain surfaces requires all components to be selected for minimal outgassing and diffusion. This necessitates the use of rare or difficult-to-machine materials with high thermal stability, while still meeting the temperature uniformity requirements. To further reduce particle generation, sources and shielding have also been refined to minimize particle load and improve serviceability while the design needs to allow for simple target exchange in production.

### Bringing it all together

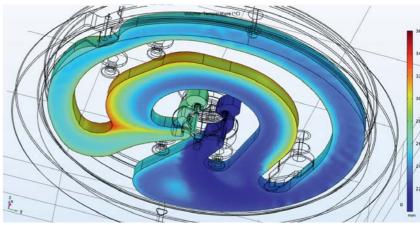

Extensive performance simulations and actual component testing on 200 and then 300mm have been at the heart of the development work (Figures 5, 6 & 7).

Solutions on 300mm are coming soon. The 300mm hardware will be ready for customer samplings within our Evatec Competence Laboratory (ECL) in Q2 2026.

Figure 5: Feasibility studies and samplings validated simulation results.

i flux [#/m2/s] at z = 97.0 mm, em. flat, x-sec slightly corrected

Figure 6: The arrangement of the FTCs combined is only one of the tuning nobs - but a major one.

Figure 7: An advanced cooling concept was necessary to deliver a reliable solution.

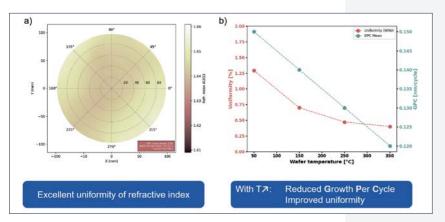

Figure 1: Single wafer process  $Al_2O_3$  layer characteristics. a) The refractive index map is shown for the 250 °C process, which shows excellent uniformity across the entire wafer at a refractive index of 1.65 in most areas. b) The thickness uniformity and GPC as a function of temperature illustrate how uniformity gets better, while GPC decreases at increasing temperature.

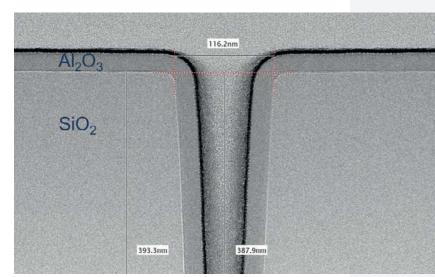

Figure 2: a) TEM measurements of  ${\rm Al_2O_3}$  on high aspect ratio structure, Large scale image of multiple vias.

Figure 2: b) Zoomed in on a 4:1 structure shows a highly conformal layer.

# Al<sub>2</sub>O<sub>3</sub> - Precise layers and high throughput

Single wafer processes, where  ${\rm Al_2O_3}$  is deposited for 25 wafers in a batch, shows excellent thickness uniformity across the 200 mm silicon substrates, with variations below 0.5% and stable refractive index values around 1.65 at 633 nm.

At a growth rate of 1.8 nm/min, 50 nm  $Al_2O_3$  coatings can be processed in under 30 min, leading to the entire batch processed within half a day, while in-film particle (>0.3  $\mu$ m) generation is kept low at < 50. Figure 1 illustrates how the refractive index, thickness uniformity and growth per cycle (GPC) behave as a function of temperature showing that elevated temperature can smoothen and densify the  $Al_2O_3$ . This can be helpful in applications such as hydrogen diffusion barriers.

Micrographs in Figure 2 also show how the process can deliver highly conformal coatings, with high aspect ratios > 4:1. Pre-etched  $\mathrm{SiO_2}$  structures were coated with 20 nm of  $\mathrm{Al_2O_3}$ , showing that the same throughput could also be achieved on structured wafers with outstanding conformality.

# AIN Films – High purity and tuneable crystallinity

Aluminium nitride is a key material in advanced microelectronic devices. It is used in piezoelectric MEMS, thermal interface layers and dielectric components for RF and power applications [1, 2]. Material quality is of the highest importance, and especially crystallinity, stoichiometry, and impurity levels which have decisive impacts on the device performance [3].

Highly oriented AIN films are typically grown using methods such as metalorganic chemical vapor deposition [4] or reactive sputtering [5]. However, these approaches often lack the process control and integration flexibility needed for modern device architectures. Whilst Plasmaenhanced atomic layer deposition offers a promising alternative [6-8], the challenge there has been to achieve similar structural quality while keeping oxygen and carbon impurities to a minimum [9, 10].

In these trials, we used our newly developed microwave-based PEALD system to grow AIN on 200 mm Si (111) wafers. The process combines trimethylaluminum (TMA) with ammonia (NH<sub>2</sub>) plasma. The highdensity microwave plasma allows precise tuning of energy input by varying the microwave power between 50-500W. Furthermore, various other parameters in the process, such as pressure, NH3 flow, and exposure time can be individually adjusted to tune the desired properties. This gives full control over film growth, chemistry and structure.

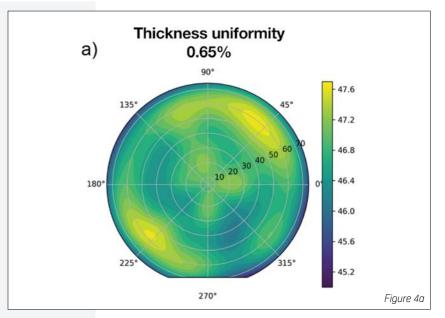

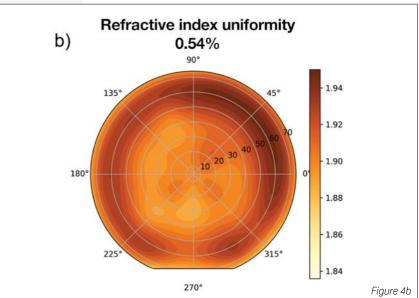

Figure 4 shows the layer characteristics as measured by ellipsometry at 633 nm. In Figure 4a, thickness uniformities <1% can be achieved at T = 200°C (chuck temperature) for a 500 cycle process. The refractive index uniformity is illustrated in Figure 4b. The wafer shows polycrystalline regions especially in the outward regions, which can be identified from high refractive indices > 1.9.

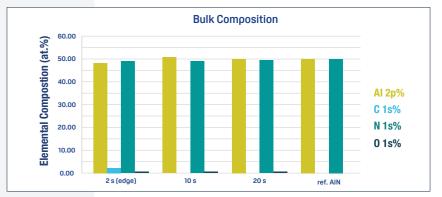

X-ray photoelectron spectroscopy

(Figure 5) confirms excellent purity,

where oxygen and carbon levels

are extremely low and almost not

detectable. Figure 5 shows the bulk

composition of AIN grown with different

plasma cycle doses at different radial

positions on the wafer. To compare the

composition, the reference values for

bulk AIN are also shown on the right

side. Of significant note is that the

AIN structure has reached an almost

identical composition to the bulk

reference case after only 10 s, which

proves its exceptional quality. There is

Figure 4: AIN layer characteristics measured by ellipsometry at 633 nm. a) Thickness uniformity

b) Refractive index uniformity. Process: 200°C, 500 cycles.

Figure 5: Elemental composition of AIN measured by XPS for different plasma times on different radial positions of the wafer. After 10s there is no C detected anymore, which is an excellent proof of high quality PEALD environment. There is only a minimal amount of oxygen detected, which is due to surface oxidation. As a reference the AIN elemental ratios (1:1) are shown.

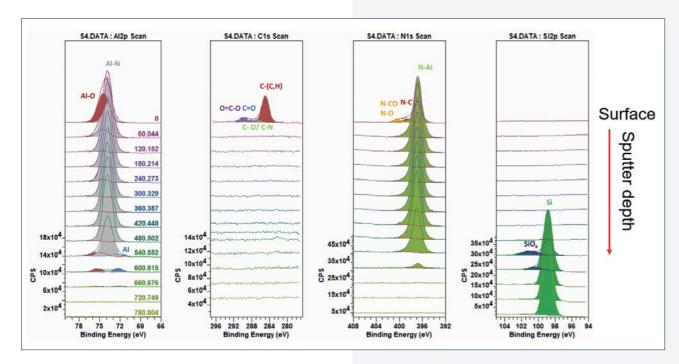

Figure 6: XPS depth profiles shown for Al, O, N, and Si. The number in different colors form purple to green show the sputter times. There is no detectable C in the bulk of the material (second plot), which is a great sign of quality nitride layers.

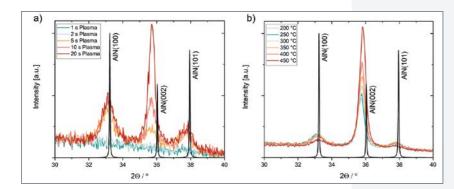

Figure 7: XRD Grazing incidence scans of processed AlN layers with different plasma times (a) and at different temperatures (b).

References: [1] La Spina, L. et al., Solid-State Electronics, 1359–1363 (2008). [2] Haider, S. T. et al., IEEE Access, 58779–58795 (2023). [3] Strnad, N. A. et al., Journal of Vacuum Science & Technology A, 40(4) (2022). [4] Demir, I. et al., Journal of Physics D: Applied Physics, 51(8), 085104 (2018). [5] Dadgar, A. et al., Physica Status Solidi (a), 220(8), 2200609 (2023). [6] Österlund, E. et al., Journal of Vacuum Science & Technology A, 39(3) (2021). [7] Ueda, S. T. et al., Journal of Materials Chemistry C, 10(14), 5707–5715 (2022). [8] Goswami, R. et al., Coatings, 11(4), 482 (2021). [9] Zhang, X. Y. et al., Journal of Materials Research and Technology, 27, 4213–4223 (2023). [10] Gungor, N. & Alevli, M., Journal of Vacuum Science & Technology A, 40(2) (2022). [11] Lau, W. S. et al., Applied Physics Letters, 87, 123505 (2005). [12] Manzeli, S. et al., Nature Reviews Materials, 2, 17033 (2017). [13] Radisavljevic, B. et al., Nature Nanotechnology, 6, 147 (2011). [14] Chowdhury, S. & Mishra, U., IEEE Transactions on Electron Devices, 60, 3060 (2013).

only minor surface oxidation caused by post-deposition air exposure. Depth profiling (Figure 6) further confirms that contamination is confined to the surface, highlighting the cleanliness and reliability of the process. We have further analysed the crystal structure using X-ray diffraction. Figure 7a shows that increasing the ammonia plasma duration enhances the (002) peak intensity, indicating stronger c-axis texture. This trend continues with higher substrate temperatures, as seen in Figure 7b. Even at just 200 °C the tool delivers highly oriented films. This level of control enables fabs to adapt the process to match their device and integration needs.

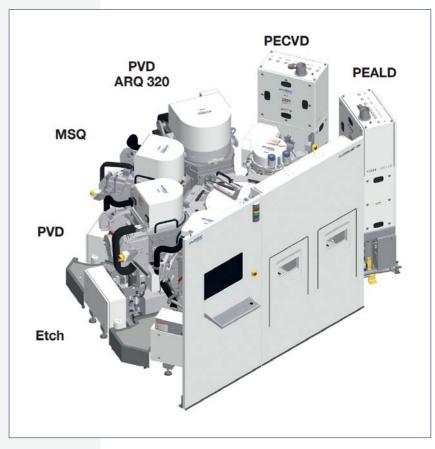

# Process integration on a single platform

One of the main advantages of the Evatec PEALD system is its integration into the CLUSTERLINE® 200 platform, where it can be combined with PECVD, sputtering, and plasma etching technologies without interrupting the vacuum process throughout the entire process flow. This configuration enables complete, multi-step device fabrication without exposing the wafer to ambient conditions.

Surface pretreatment, seed layer deposition, film growth and encapsulation can be carried out in a connected and controlled vacuum and process flow. This high degree of integration opens new options for advanced device fabrication, e.g. high-к metal gate stacks (HKMG) benefit from clean, sequential deposition of dielectrics and metals in one tool environment [11]. 2D materials like MoS, and graphene need damagefree surface pretreatment and careful encapsulation to retain their electrical performance [12,13]. GaN on diamond for high power devices relies on lowtemperature, conformal coatings with tight interface control [14]. VCSELs and Micro-LEDs require precise control of multilayer thickness and stress for optimal optical performance.

Figure 8 shows a possible configuration of the CLUSTERLINE® 200 with PEALD, PECVD, sputter, and etch modules connected to a central wafer handling system. Each module can be adapted for specific materials or coating processes. Depending on requirements, the system can be equipped with multiple PEALD modules with numerous precursor lines.

### So what's next?

The Evatec team is already exploring advanced materials such as AIScN, InGaN etc. and how a newly developed RF chuck can tune crystallinity and other important properties through super-cycle processing. With all these capabilities in one platform, we are ready to support our customer's innovations in logic, power devices, optical coatings, optoelectronics and sensor technologies from R&D to high-volume manufacturing.

Acknowledgement: XPS measurements have been performed at the Luxembourg Institute of Science and Technology.

Figure 8: CLUSTERLINE® 200 combines many advanced technologies for advanced device fabrication without breaking vacuum.

"With this new platform, Evatec brings a highly flexible and scalable PEALD solution to the market. It delivers high-purity, crystalline AIN films on full 200 mm wafers. The tool is ready to support a wide range of applications, from next-generation piezoelectric components to thermal and dielectric layers in RF and power devices. For customers looking to combine high performance with process control, this system offers a clear path forward"

Dr. Julian Pilz, Silicon Austria Labs (SAL)

Elghazzali, Manager Technology Development, Stanley Low, Product Marketing Manager, and Admir Asanoski, Head of Semiconductor & Advanced Packaging, expand on Evatec strategy and roadmaps, making sure our market offerings can address the full spectrum of customer requirements.

Advanced Panel Level packaging enables higher bandwidth and improved thermal management, both of which are critical for Al chiplets. Moving from Wafer Level Packaging (300 mm wafers) to panel formats such as 310x310 mm, and extending solutions to larger areas up to 650x650 mm, is part of the evolution that Evatec is ready to enable with its platforms.

Evatec's CLUSTERLINE® platform is already established for high-volume deposition and etching in wafer and panel manufacturing. Building on this foundation, we are extending the platform's capabilities to meet the new requirements of advanced packaging. Our roadmap covers three key areas where we are investing and developing future solutions.

# Building on a proven base

The Panel Level Packaging (PLP) market is entering a phase of rapid growth and innovation, driven by modular chiplet architectures for Al and high-performance computing. Evatec has been shaping the future of Panel Level Packaging from the very beginning. Almost a decade ago, when this new market segment first emerged, Evatec pioneered panel level PVD solutions right from the start. Today, the company is leveraging its long-standing expertise and strong market presence to drive the next wave of innovation. With a comprehensive roadmap in place, Evatec is continuing to adapt its technologies and product portfolio to the latest developments and future trends, starting from the first projects on 310x310 mm panel formats, then advancing towards even larger panel sizes.

Our activities focus on redistribution layer (RDL) and backside metallization (BSM), through-glass via (TGV) technologies, and reactive ion etching (RIE) for PCB and IC substrate manufacturing.

### RDL and BSM roadmap for AI chiplets

Evatec has launched its first dedicated PLP development oroject for the 310x310 mm format starting from the CLUSTERLINE® 300 platform. This modified system is being engineered to handle and transport panels efficiently, providing higher substrate utilization per cycle compared to 300 mm wafers. Such scaling will allow larger AI chiplets and high-bandwidth memory (HBM) stacks to be processed, boosting throughput and reducing cost per chip.

The development includes new DC/RF sputter and etch modules, a high-performance source and magnet system, and in-situ process control for maximum uniformity and optimized material use. Capabilities under development also target precious metal deposition such as gold with focus on reducing target costs.

The 310x310 mm solution is expected to be available to foundries and OSATs by 2026. In parallel, Evatec is preparing cost-optimized solutions for larger panel formats on the CLUSTERLINE® 600, supporting sizes up to 650x650 mm.

| Wafer  | Panel      | Platform         |

|--------|------------|------------------|

| 300 mm |            | CLUSTERLINE® 300 |

|        | 300x300 mm | CLUSTERLINE® 310 |

|        | 310x310 mm | CLUSTERLINE® 310 |

|        | 510x515 mm | CLUSTERLINE® 600 |

|        | 600x600 mm | CLUSTERLINE® 600 |

Evatec solution of optimal efficiency

### TGV technology roadmap for large panels

Glass interposers are becoming essential for high-frequency and RF packaging. They require precise drilling, metallization, and dielectric gap filling. Evatec's CLUSTERLINE® 600 platform is being prepared for advanced thin-film deposition on large-area glass substrates.

The roadmap foresees adhesion layer and cooper seed layer deposition for TGVs with aspect ratios up to 6:1, with future enhancements aiming beyond 10:1. Ionized plasma capabilities will support conformal adhesion and copper coverage along the sidewalls enabling robust interconnect performance.

In addition to deposition modules, the roadmap includes process integration, automated metrology, and advanced panel-handling concepts (such as enhanced flipper systems) to deliver a complete TGV processing solution for panels up

# RIE and Desmear roadmap for PCB/IC substrates

For organic, polymeric, and glass substrates, Evatec is extending its technology base with plasma etching and desmear solutions. The CLUSTERLINE® 600 and the CLUSTERLINE® 310 with integrated CCP etch modules and atmospheric batch degassing will support advanced substrate pre-treatment.

Planned configurations will enable deep via etching with high aspect ratios and desmear processes optimized for polymer and SiO<sub>2</sub> fillers. Balanced chemistries and Arctic cooling techniques will ensure residue-free via walls, reliable copper adhesion, and repeatable performance across large panels. These developments will provide customers with scalable, production-ready solutions for the evolving demands of advanced PCB and IC substrate manufacturing.

### Outlook

With the 310x310 mm project underway and larger-format developments in preparation, Evatec is establishing a roadmap that addresses the full spectrum of future PLP requirements.

Our CLUSTERLINE® platforms will continue to evolve as flexible, high-volume manufacturing solutions, supporting customers as they move from wafer-based packaging to panel formats of increasing size and complexity.

32 | LAYERS 9 LAYERS 9 | 33

# Welcome to

# Advanced Directional Sputtering (ADS)

Evatec's Senior Program Manager, **Kai Wenz**, introduces the latest PVD technology capability in Evatec's portfolio and gives us a flavor of some of the markets where the enhanced capability can help deliver new levels of device performance.

# Conventional PVD – an industry workhorse

Standard physical vapor deposition (PVD) sputtering is a workhorse technique across all Evatec market segments. In the conventional way, atoms are ejected from a target by energetic ion bombardment and travel towards the substrate in a largely random, isotropic distribution. For planar films or shallow topographies, this solution works well - deposition is fast, uniform, and cost-effective. However, as device architectures have evolved toward smaller geometries, higher aspect ratios, and increasingly 3D layouts, the limitations of standard sputtering have become apparent. In deep features such as through vias, or trenches, Isotropic particle flux tends to:

- Deposit excessively on feature sidewalls, narrowing or closing the opening before the bottom sidewalls are coated.

- Increase the probability of voids.

- Result in incomplete or discontinuous bottom coverage, leading to electrical open circuits or high resistance.

# Solving the 3D and high aspect ratio challenge

Directional sputtering addresses these challenges by engineering the angular distribution of sputtered atoms so that they arrive predominantly at almost vertical incidence on the substrate surface. This is achieved using methods such as:

- Collimated sputtering: Placing a physical collimator between the target and the substrate to filter out off-angle atoms.

- Ionized PVD (I-PVD): lonizing a significant fraction of the sputtered flux and using an electric field to direct it straight into the features.

- Long-throw sputtering: Increasing targetto-substrate distance to naturally narrow the angular spread of incoming atoms.

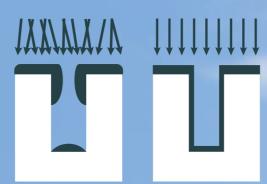

Figure 1: Conventional vs directional sputtering.

### The Evatec solutions - SDS and ADS

Evatec's ADS stands for Advanced Directional Sputtering and is available for the CLUSTERLINE® 200 and 300 platforms.

ADS is a key development focus for our new frontend capabilities, allowing high productivity with shutter, RF Bias, hot and cold electrostatic chucks at very low particle and metallic contamination levels. For less challenging structures, aspect ratios and technology nodes the simplified SDS (Standard Directional Sputtering) setup with fewer tuning features is available for cost effectiveness.

Key materials are Ti/TiN, Ta/TaN, and Cu, but it can be used and optimized for other materials too.

In today's advanced manufacturing landscape, where structures can be smaller, pitches tighter, and sometimes deeper, with higher performance demands, directional sputtering has moved from a specialty process to a critical enabler. Without it, many state-of-the-art metallization steps in high-performance computing, 5G, and AI (artificial intelligence) hardware would not be manufacturable at volume with the required reliability.

ADS 200 solution for 200mm processing

ADS 300 solution 300mm processing

Figure 2

### **ADS in action**

Here are just four application examples where directional sputtering is essential in supporting our customers and their needs:

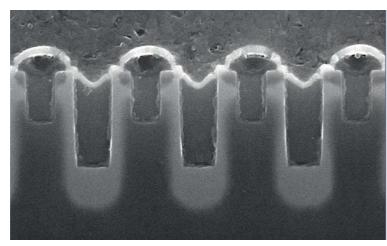

### 1. Power Discrete

In trench MOSFETs and IGBTs, Ti/TiN layers must form a continuous adhesion and diffusion barrier deep inside high-aspect-ratio trenches. Standard sputtering often causes sidewall overhang and poor bottom coverage, leading to high resistance and reliability issues. Evatec's ADS solution overcomes this challenge.

Sic Mosfet Gate Design - Die Cross Section, SEM View from Rohm Semiconductor -Source: SiC Transistor Comparison 2023 report, Yole Group

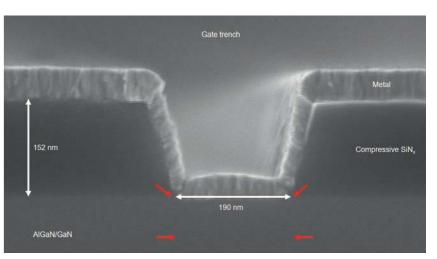

### 2. Wireless

GaAs-based HBTs and HEMTs are the most commonly used technologies for RF power amplifiers. These devices require conformal coatings of metals like WTi, Cu, Au, and Ti, especially Ti/Cu and Ti/Au bi-layers, where Ti serves as a seed layer and Cu or Au as the conductor. ADS technology provides superior conformality and step coverage compared to traditional sputtering, enabling damage-free deposition on complex structures. Its precise plasma control and low ion energy ensure excellent film uniformity and adhesion, enhancing device performance and reliability in demanding RF environments.

### 3. Frontend

In advanced interconnect fabrication, liner, barrier layers, and seed layers must be continuous and uniformly coated on the sidewall. Depending on the architecture, coating at the bottom may also be required for connection to other features underneath. Typical materials used are Ti/TiN-AI (200 mm) reflow or TaN/Ta-Cu (300 mm) enable void-free Cu electroplating. Typical structures used are contact holes, trenches and dual damascene features. With the trend to smaller structures new materials are under evaluation and the number of interconnects continues to increase.

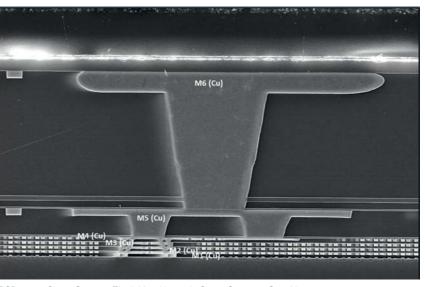

### 4. Advanced Packaging

For Through-Silicon Via (TSV) seed layers in advanced interposers, continuous metal coverage of typical Ti-Cu to the bottom is mandatory for reliable Cu electroplating. It becomes challenging for standard sputtering to establish a conductive path for higher aspect ratios and via depths, whereas directional sputtering ensures full continuity. In more highly integrated devices, advanced packaging is becoming even more important.

BCD 90MN Cross-Section: Thick metal layer in cross-section - SEM view Exploration of hightemperature PECVD SiNx for strain engineering of GaN-HEMTs | Ferdinand-Braun-Institut. Image courtesy of © FBH

BCD 90nm Cross-Section: Thick Metal Layer In Cross-Section - Sem View Source: BCD Comparison 2024 Report, Yole Group

SK Hynix HBM3 – HBM DRAM die: package cross section, SEM view © Yole Group 2025

SK Hynix HRM3 -Bumps: package cross section, SEM view © Yole Group 2025

# Want to know more?

Got a challenging application? Want to investigate sampling opportunities in Evatec's Competence Laboratory (ECL)? Contact your local Evatec sales and service organization to find out more.

36 | LAYERS 9 LAYERS 9 | 37

**SEMICONDUCTOR & ADVANCED PACKAGING**

| 300mm fronteno integration                                                              |   |

|-----------------------------------------------------------------------------------------|---|

| ADVANCED PACKAGING                                                                      |   |

| Welcome to small panel processing – up to 310x310 mm!                                   |   |

| Development of a highly sensitive test vehicle                                          |   |

| POWER DEVICES                                                                           |   |

| Enabling robust SiC power device fabrication with amorphous-carbon sputtering           | į |

| SOLARIS® – Increasing throughput for thick aluminum layers in power device applications | Į |

| Doworing the SiC future                                                                 |   |

38 | LAYERS 9 LAYERS 9 | 39

# 300mm frontend integration

# Reaching for the sky

As the semiconductor industry evolves, it continues to follow two key innovation paths: "More Moore", focusing on continued transistor scaling and performance improvements, and "More than Moore", targeting functional diversification through advanced packaging and integration of different technologies.

Admir Asanoski, Head of Business Field Semiconductor and Advanced Packaging, and Kai Wenz, Senior Program Manager Technology Development, explain how Evatec supports both strategies with new innovative solutions.

# The move to smaller feature sizes is relentless

With 2D scaling reaching physical limits, new strategies such as 3D integration, novel materials, and innovative device architectures are essential to meet the demands for higher logic density and multifunctional system performance. These trends demand increasingly sophisticated thin-film depositior capabilities, enhanced contamination control, and improved process reliability. Figure 1 illustrates the big picture where capabilities required for both strategies come together to satisfy increasingly complex device needs.

### CLUSTERLINE® 300 – Building on a strong foundation

Evatec set the baseline back in 2022 for its initial planar frontend capabilities by having the right hardware in place through its CLUSTERLINE® 300 platform. Since that time we have been focused on an extensive program in advanced directional sputtering (ADS) to enable small feature sizes and more complex architectures. Figure 2 illustrates the principle of how we build a final solution optimized for mass production in the market combining hardware and process know-how.

We can already offer qualified processes for frontend planar layers like Ti, TiN, Al alloys, Ta and TaN at very low particle levels and layers free of metallic contamination. We can now also support next generation materials e.g. Ruthenium. We are continuing on our road of process development offering Standard Directional Sputtering (SDS) for lower aspect ratios (AR) up to 5:1 and via and trench structures with critical dimensions (CD) >110nm suplemented by Advanced Directional Sputtering (ADS) for higher performance and aspect ratios up to the limit of PVD for via and trenches CD >35nm.

# Functional Density Functional Density

Figure 1: The Big Picture: Innovations for future essential chips.

Combining our current markets with frontend technologies

Figure 2: CLUSTERLINE® 300 – a strong foundation on which to build customer solutions.

| Items                    | Conventional   | High              | -End           |

|--------------------------|----------------|-------------------|----------------|

|                          |                | Standard (SDS)    | Advanced (ADS) |

| KEY FEATURES:            |                |                   |                |

| HOT/COLD ESC             |                |                   |                |

| SHUTTER                  |                |                   |                |

| WiW RS/THK uniformity    | <5%            | <3%               | <3%            |

| Target-Subtrate Distance | short          | short /mid        | long           |

| Structures               | Planar, Reflow | CD >110nm /AR 5:1 | CD >35nm       |

| Shutter                  | Yes            | Yes               | Yes            |

| 300mm hot/cold ESC       | Yes            | Yes               | Yes            |

| DC Sputter power         | DC             | DC                | DC             |

|                          | DC pulse       | DC pulse          | DC pulse       |

| RF chuck bias            | Yes            | Yes               | Yes            |

|                          |                |                   |                |

Figure 3: A range of solutions according to application demands.

# CLUSTERLINE® 300 process modules

The current solutions available can be split into "conventional" and "high-end" frontend (see Figure 3). The conventional setup is focused on the best target utilization using long-life targets beneficial for thicker layers, whilst highend solutions for thin layers are tuned for performance for each application.

In all cases, however, configurations are equipped with the same common capabilities such as shutters for cleaning and chamber preparation, hot/cold electrostatic chucks for full temperature control with full-face deposition, and supported by additional frontend reoptimized ICP etch chambers with  ${\rm H_2}$  capabilities, and high pressure degas and cool chambers.

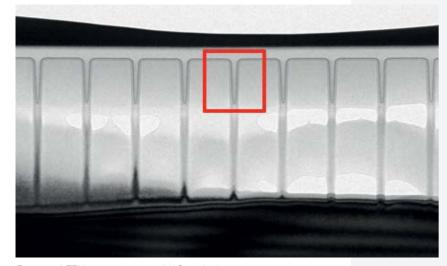

Besides good WiW and WtW uniformity, the SDS solution can also deliver via nanostructures up to 5:1 AR with good step coverage performance (Figure 4). Further enhancement of performance will come with an ADS solution. Performance for trenches is typically even better by minimum factor of 1.5 compared to vias.

Mechanical particle levels can be controlled typically to levels in the range <20adders for sizes >60nm with metallic contamination controlled to <1.0E+10at/cm² for the standard frontend materials.

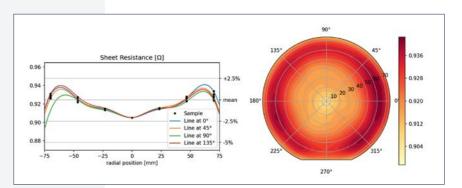

Productivity depends on the process flow. It can reach up to 50wph on a fully-equipped next generation CLUSTERLINE® 300 platform for TiAl deposition for memory applications. It achieves a barrier for Al through a 10nm thin Ti layer with excellent surface quality that avoids spiking into the silicon through full process control of our electrostatic chucks, pre- and post-treatments (Figure 5).

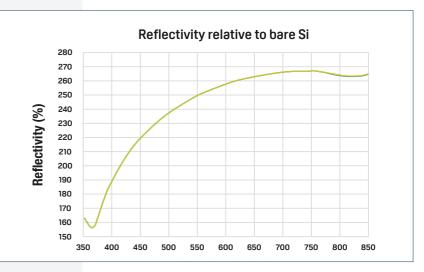

For different applications such as high bandwidth memory this Al layer can be temperature stress stable to achieve wafer bow always below <200µm. We have in-house sampling capabilities for Ti, TiN, Al-alloys, Ta, TaN, and Cu including pre- and post-treatment like high pressure degas, cool, and ICP Etch (Ar and/or  $\rm H_2$ ). In-house metrology techniques include sheet resistance, thickness, particles, XRD, SEM /FIB, reflectivity (see Figure 6). Please also ask us about other materials for processing in basic and SDS module configuration.

There are many more exciting developments still to come on 300mm. Knowing that this is not the end, we already plan our next steps by adding the CVD and ALD capabilities that exist already on our 200mm platform to CLUSTERLINE® 300 too e.g. for high-end directional sputtering (HDS) and nanostructures <35nm where PVD on its own will no longer be sufficient. You can also read more about our ALD developments on page 26 in this year's LAYERS.

The new developments for ADS and beyond will also include the development of a new cluster platform that will allow more single process chambers to be added to one platform fulfilling the solution needs that are planning to be released together with the final ADS solution. All these new developments will bring Evatec to the next level as a semiconductor solution provider, preparing for a future where we really can reach out for the sky together with our customers.

If you would like to learn more about what we are doing including accessing the capabilities within our ECL process laboratory, please "reach out" too! Simply contact your local Evatec service organization.

| Structure<br>dimensions | Diameter 110nm<br>Depth 450nm | Diameter 160nm<br>Depth 450nm | Diameter 250nm<br>Depth 450nm |

|-------------------------|-------------------------------|-------------------------------|-------------------------------|

|                         | Average %                     | Average %                     | Average %                     |

| Top Sidewall            | 19%                           | 46%                           | 43%                           |

| Middle Sidewall         | 10%                           | 32%                           | 27%                           |

| Low Sidewall            | 10%                           | 33%                           | 29%                           |

| Bottom                  | 32%                           | 17%                           | 28%                           |

|                         |                               |                               |                               |

Figure 4: SDS Step coverage performance.

Figure 5: Excellent TiAl layer surface quality

| Reflectivity refer to Si @436nm | Result |

|---------------------------------|--------|

| Center                          | 212%   |

| Edge                            | 212%   |

| Range                           | 0.05%  |

Figure 6: Reflectivity performance of TiAl layer

# Welcome to small panel processing – up to 310x310 mm!

Since the launch of our first panel sputtering equipment in 2016, Evatec has become a leading supplier during early "take-up". As the panel size has not really been standardized, our CLUSTERLINE® 600 has given high flexibility in this regard and can be configured based on the customer specific format going up to 650x650 mm. Our Head of Semiconductor & Advanced Packaging, **Admir Asanoski**, answers questions about the latest developments at Evatec when it comes to small panel processing for 300x300 mm or 310x310 mm.

# What is driving the demand for 310x310 mm solutions?

In general, panel-level packaging (PLP) offers better material utilization than wafer-level packaging (WLP), leading to overall cost reductions regardless of size. The growing demand for smaller panels, such as 310x310 mm, is primarily driven by Artificial intelligence (AI) and high-performance computing (HPC) applications.

Smaller panels enable tighter control of critical dimensions and overlay accuracy, which is essential for these advanced applications. They also deliver higher yields thanks to reduced warpage, lower mechanical stress, and lower defect density compared to larger panels.

That said, demand for larger panel formats will continue to expand in parallel, particularly for mobile devices and next-generation IC substrate applications.

# What experience do we already have for 310x310 mm solutions?

We are already delivering proven solutions for both 300x300 mm and 310x310 mm formats based on our CLUSTERLINE® 600 platform. Customers value that this equipment and the associated processes are well-established in production environments and can be easily adapted for smaller panel sizes.

Another key advantage is the panel size flexibility our system provides, a major factor in customers choosing this solution.

Looking ahead, we are exploring multi-panel handling capabilities that would enable processing of up to four small panels simultaneously, supporting customers as they scale their production capacity to the next level.

# What's the approach to the new tool and what can customers expect?

In many ways, the new dedicated platform is primarly the result of an engineering effort rather than a new development project. It combines the proven strengths of our 12-inch wafer equipment "CLUSTERLINE® 300 \$ HEXAGON" and our panel system "CLUSTERLINE® 600", incorporating the necessary adaptations for the smaller panel size.

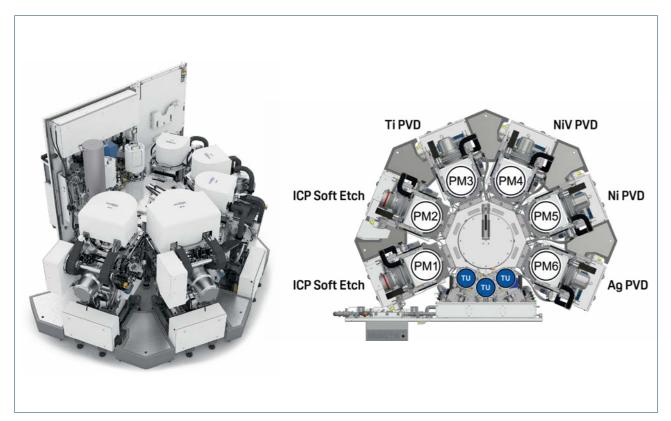

The system is built on our existing cluster wafer platform, ensuring the smallest possible footprint. This platform has already been production-proven in applications such as Backside Metallization (BSM) as a Thermal Interface Material (TIM) for heat dissipation, BSM / Frontside Metallization for power devices, optical coatings, and many other processes.

By integrating our established degas pre-treatment and Arctic Etch technology, customers can achieve rapid process integration for their specific small panel sizes while maintaining the same high performance and reliability as our existing systems.

This development marks an important milestone for Evatec, enabling customers to rely on a single source for both wafer and panel-level solutions. In addition to Ti/Cu RDL seed deposition, the new platform will also support our BSM / TIM process, featuring a highly efficient gold (Au) source that reduces target investment compared to conventional flat targets.

# So why now develop a dedicated 310x310 mm tool?

While the CLUSTERLINE® 600 offers clear advantages and has proven its versatility in processing smaller panels, there are certain trade-offs that motivated the introduction of a dedicated small panel equipment.

Key drivers include footprint constraints, cleanroom cost considerations, and the need to optimize initial CAPEX investment for our customers.

This new tool will expand our panel-level product portfolio, providing customers with greater flexibility and the ability to select the system that best matches their production requirements and strategic goals.

# How are you fast tracking the project?

To accelerate the engineering of the new system, we are leveraging our existing designs, proven technologies, and established supplier network. A strategy that ensures a fast time-to-market while maintaining the highest quality standards. Equally important, we are working closely with customers, involving them from the beginning, to ensure that all technical and operational requirements are met prior to delivery. A smooth installation and ramp-up phase is also an essential topic. This will be supported by our local Sales & Service Organizations (SSOs), who already have extensive experience with the existing platforms. In addition, we provide comprehensive customer training and on-site support (see article on page 12, LAYERS 9) from Evatec specialists to guarantee a seamless transition into high-volume production.

# How can customers find out more about the tool and explore how it can meet their needs?

Customers can contact their local SSO for details on the tool, timelines, and how it fits their needs.

# **Advanced Packaging**

### **CLUSTERLINE® 600**

### HEXAGON

# **CLUSTERLINE® 300**

**Panel Level**

Wafer Level 300 mm

Combining all strengths in one dedicated platform

## **EVATEC SOLUTION CLUSTERLINE® 310**

- The base will remain and be used from our wafer equipment CLUSTERLINE® 300

- First application –

RDL with 480 mm planar targets

- Second application BSM with special source for Au

# Development of a Highly Sensitive Test Vehicle for the Accurate Measurement of Seed Layer Contact Resistance in 2.0 µm-diameter Vias

### Abstract

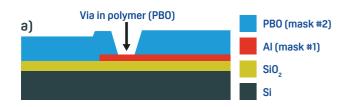

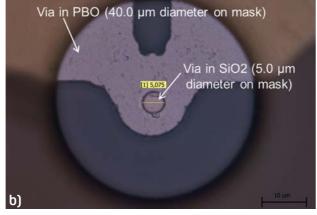

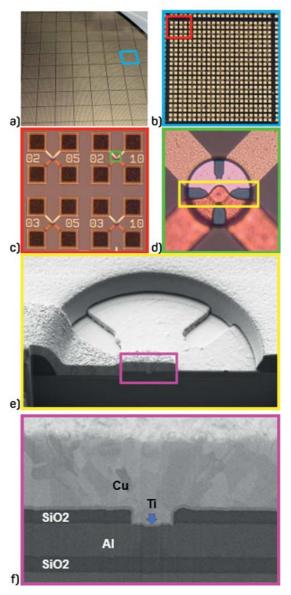

In the increasingly sophisticated semiconductor packaging landscape, multiple dies can be connected side-by-side on an interposer or stacked vertically to achieve shorter distances and higher interconnects density. These technologies allow the Heterogeneous Integration of chiplets with increased functionality, higher speed and better power efficiency. The high interconnects density and the concomitant shrinkage of the critical dimensions (e.g. RDL width/pitch and diameters of the vertical interconnections), increase exponentially the importance of the contact resistance between metal interfaces. In wafer-level packaging, interconnects are commonly manufactured by sputter deposition of a seed layer followed by Cu electroplating. The main challenge, prior PVD, is the elimination of the native oxide present on the exposed metal contacts, coupled with the presence of organic load released by the polymer dielectrics widely used in WLP (e.g. Pl and PBO) that contaminates the process chambers of the PVD platform.

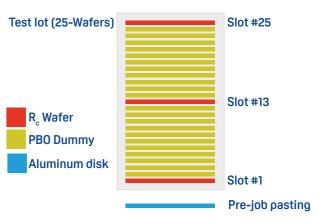

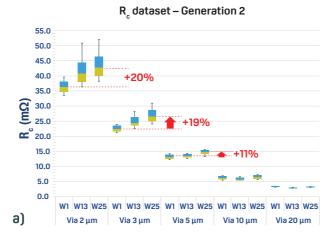

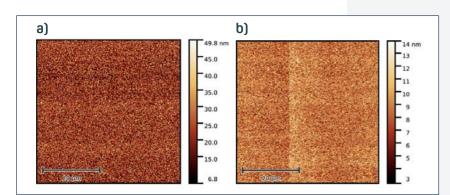

This work presents an improved wafer-level manufacturing process for fabricating Kelvin resistors based on Al/Ti/Cu metallization and via diameter ranging from 2.0 µm up to 20.0 µm. Experimental R<sub>a</sub> data have shown that the sensitivity of the fabricated structures, in regard of the chamber conditions, is inversely proportional to the contact area. A test run of 25 wafers processed at a throughput of 55 wafers/ hour on the HEXAGON has revealed a constant R<sub>2</sub> on 10.0 and 20.0 um via structures, but instead a significant excursion on the smaller vias. For example, 2.0 µm via structures exhibited  $R_a = 36.5 \text{ m}\Omega$  on wafer#1 and  $R_a = 44 \text{ m}\Omega$  on wafer#25. This corresponds to a 20% increase within lot. In conclusion, the fabricated Kelvin resistors are very suitable test vehicles to be used for benchmarking PVD seed layer processes and to establish optimum conditions ensuring high yield and a constant wafer-to-wafer quality in next-generation highdensity interconnects WLP applications.

Patrick Carazzetti \* - Evatec Ltd. | Trübbach, Switzerland | patrick.carazzetti@evatecnet.com

Kay Viehweger - Fraunhofer IZM-ASSID | Moritzburg, Germany | kay.viehweger@assid.izm.fraunhofer.de

Carl Drechsel - Evatec Ltd. | carl.drechsel@evatecnet.com

Ewald Strolz - Evatec Ltd. | ewald.strolz@evatecnet.com

Jürgen Weichart - Evatec Ltd. | juergen.weichart@evatecnet.com

Copyright IEEE. Recreated with permission, based on content originally published at the International Conference on Electronic Packaging Technology (ICEPT).

### Introduction

The increasing demand for devices with higher speed and increased power efficiency, fueled by High-Performance Computing (HPC) and Artificial Intelligence (AI), is driving tremendous innovations in the electronics industry, both in frontend-of-line (FEOL), but even more in the field of advanced packaging [1]. TSMC's Chip-on-Wafer-on-Substrate (CoWoS) [2,3] and ASE's Fan-Out-Chip-on-Substrate (FOCoS) [4,5] are two examples of cutting-edge wafer-level packaging (WLP) technologies. Both combine multi-level fine-pitch redistribution layers (RDL) with shorter interconnect lengths and microbumps to enhance signal speed and power efficiency in 2.5D and 3D architectures. These technologies offer the advantage of a larger package size and more I/O connections per unit area. In addition, horizontal 2.5D and 3D stacking configurations of components enable the Heterogenous Integration of various processor and memory modules layer by layer, e.g. logic System-on-Chip (SoC) and High-bandwidth Memories (HBM) on the same IC platform [6,7].

Latest developments in advanced WLP applications often require RDL technologies with critical dimensions below 10 micrometers [8,9]. Therefore, a tight control of the contact resistance ( $R_{\rm c}$ ) is becoming increasingly important in high-volume manufacturing (HVM) to ensure high yield and a constant wafer-to-wafer quality. The smaller scaling of the interconnects is coupled with the presence of high loads of volatile contaminants released by the organic passivations widely used in WLP. The latter are typically spin-coated films of Polyimide (PI) or Polybenzoxaxole (PBO). State-of-the-art packaging platforms require the implementation of advanced strategies to mitigate the impact of hydrocarbon species and oxide contamination on the metal interfaces to avoid an adverse impact on  $R_{\rm c}$  [10-13].

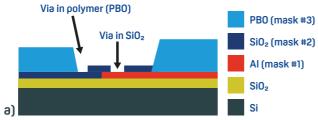

This work presents a wafer-level manufacturing process for the fabrication of Kelvin resistors based on the interface between a bottom Al electrode and an upper Ti/ Cu metallization. A 5.0  $\mu$ m-thick PBO passivation is present on the wafer, separating the two metallization levels, for mimicking the organic load of real WLP products. Various Kelvin structures with via diameter ranging from 2.0 to 20.0  $\mu$ m have been designed. The smaller the via size, the higher the sensitivity of the structure in regard of process parameters and chamber conditions. The fabricated Kelvin resistors are suitable test vehicles to be used for monitoring the performance of the PVD process based on different throughput and conditioning frequency. The goal is to establish a set of optimum conditions that allow to keep low and stable R for a given via size at the highest throughput.

In a multi-level interconnects scheme, such as CoWoS and FOCoS, the PVD stack is present at numerous interfaces: (1) between the chip I/O's (i.e. Aluminum pads), and the first RDL, (2) between multi-level RDLs and (3) between the uppermost RDL and the under-bump metallization (UBM). The quality of these interfaces plays a fundamental role in the overall electrical device performance in terms of power consumption and signal integrity.

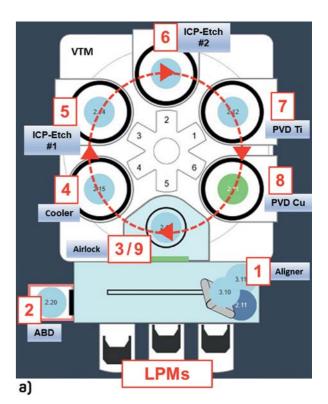

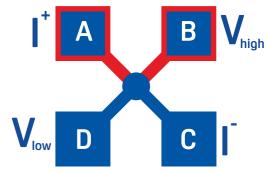

| LPMs |                  |  |

|------|------------------|--|

| 1    | Aligner          |  |

| 2    | Atm. Batch Degas |  |

Figure 1: a) State-of-the-art 300 mm HEXAGON used in high-volume manufacturing of wafer-level

b) Corresponding process flow that includes wafer pre-treatment steps and the deposition of adhesion and seed layers.

b)

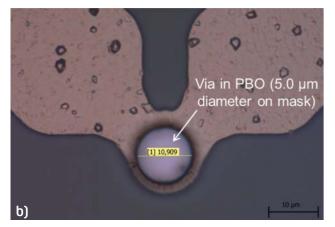

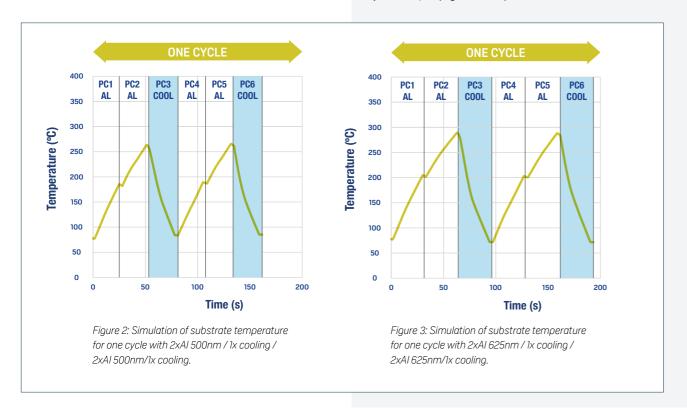

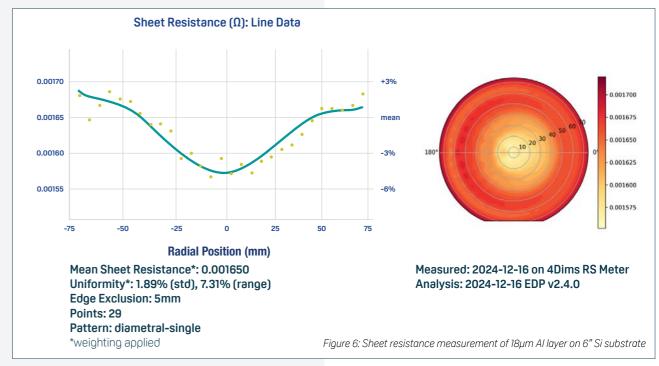

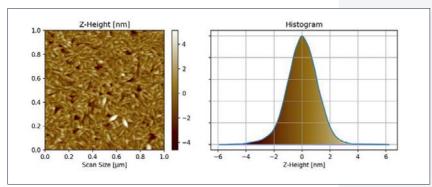

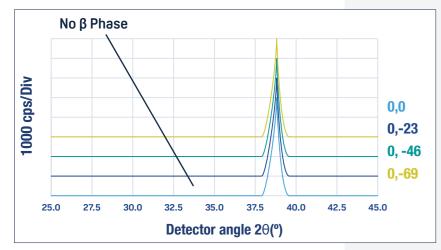

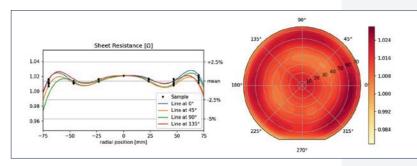

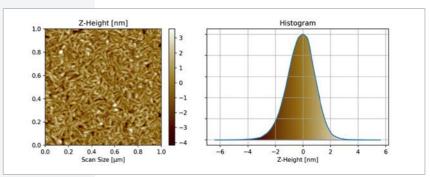

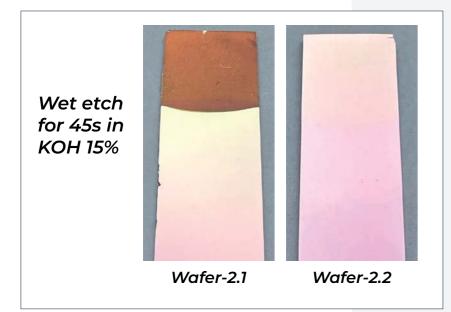

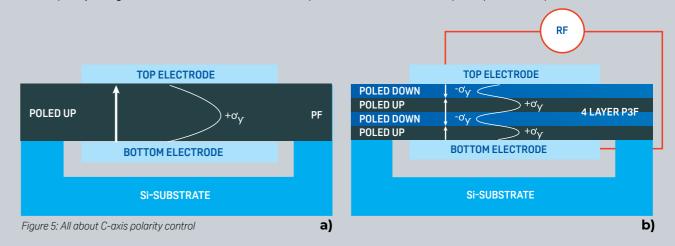

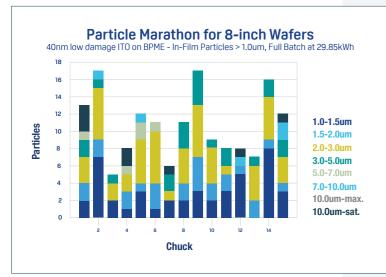

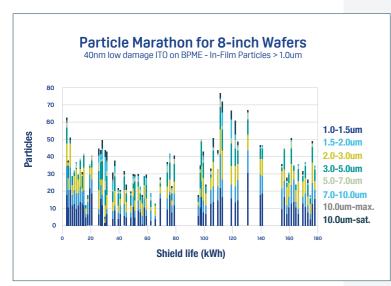

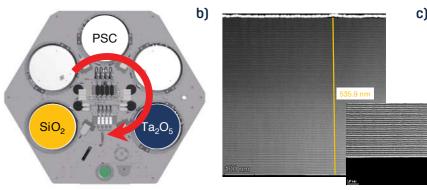

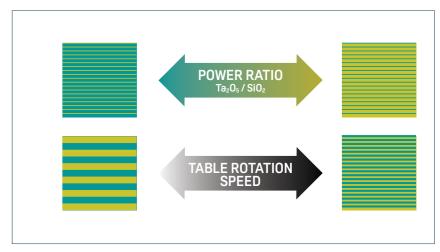

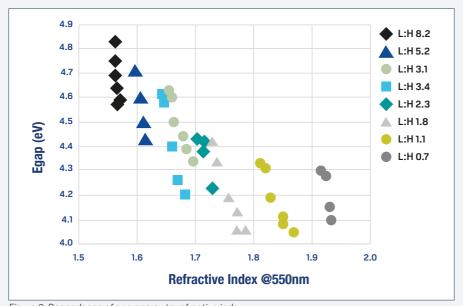

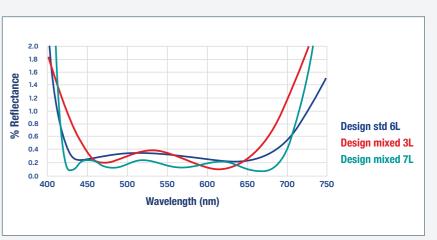

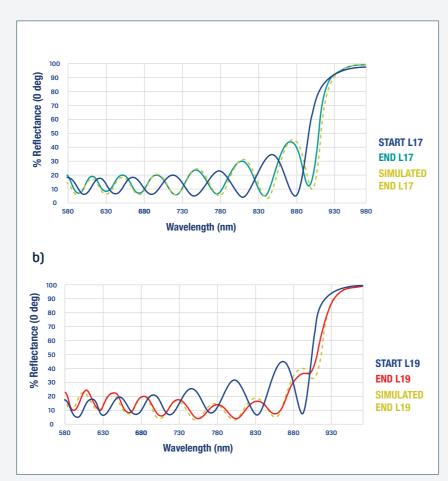

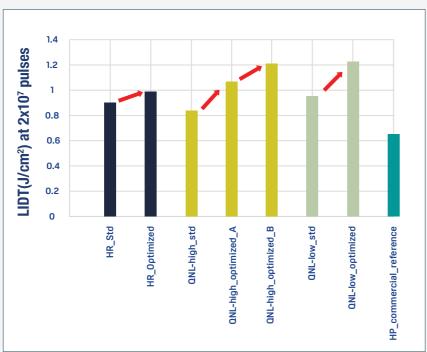

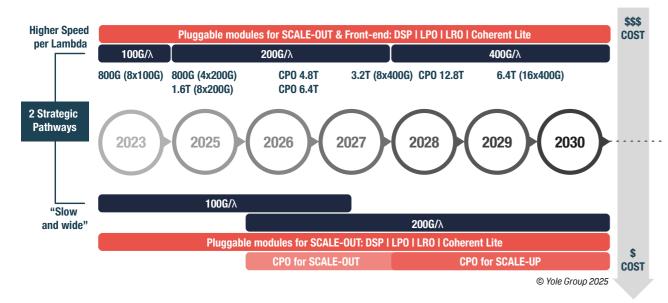

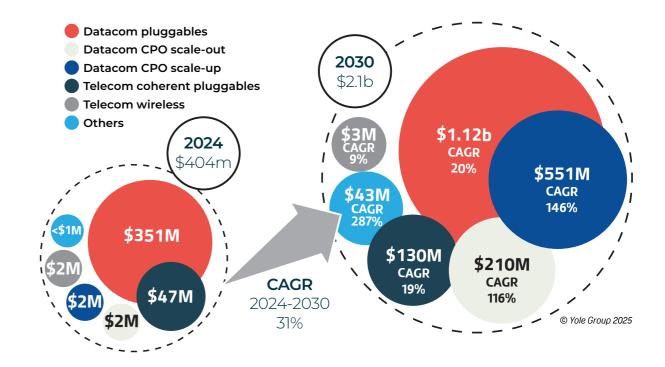

packaging,