NORTH AMERICAN EDITION

# ADVANCED PACKAGING

WLP, hybrid bonding and chiplets

# **SEMICONDUCTOR**

Solving thin film challenges across 3D ICs, SiC Power & Wireless applications

# **OPTOELECTRONICS**

From expertise in ITO to the future of Mini & Micro LED – technology & market updates

# **PHOTONICS**

Thin film knowhow in Augmented Reality & Edge Emitting Lasers

# Contents

# 02-03 Welcome

From stronger supply chains to platforms with new capabilities, CEO Andy Waelti tells us about the actions taken by Evatec to be ready for whatever our customers demand in 2023 and beyond.

# 04-19 Corporate

Get some quick facts about our company, find out more about our European and North American organizations and learn how our retrofit team is helping customers get even more out of their existing Evatec tools.

# 20-39 Advanced Packaging

Learn about chiplet technology from guest author Jan Vardemann, how to control stress in low temperature deposition processes for SiC and SiCN in hybrid bonding applications, and how Evatec's new HEXAGON takes us one step closer to perfection in wafer level packaging applications.

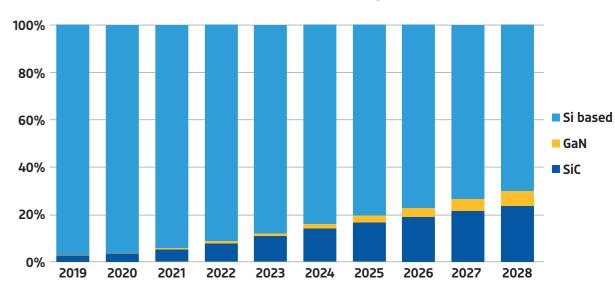

# 40-59 Semiconductor

Meet the latest members of the growing Business Unit team and read a selection of market and thin film technology news stories across Front End Integration, Power and Wireless applications.

# 60-73 Optoelectronics

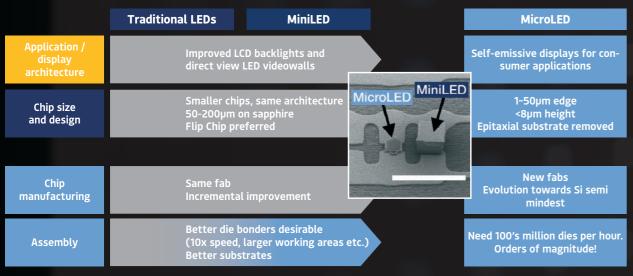

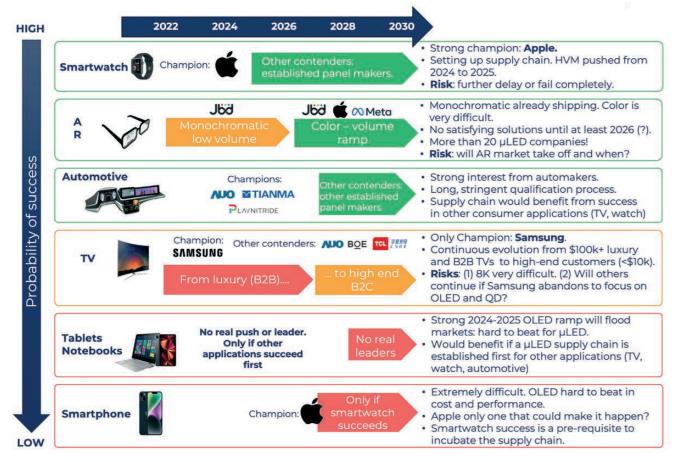

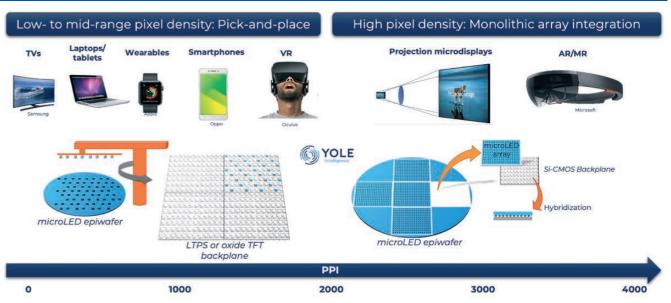

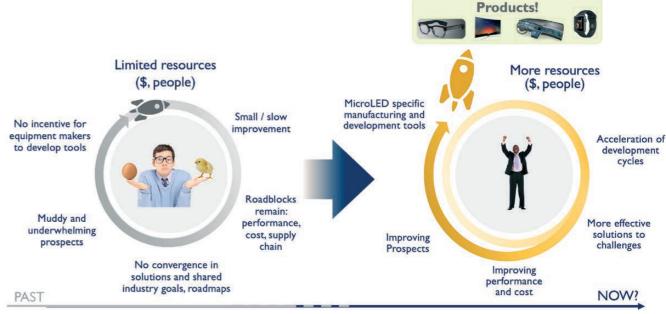

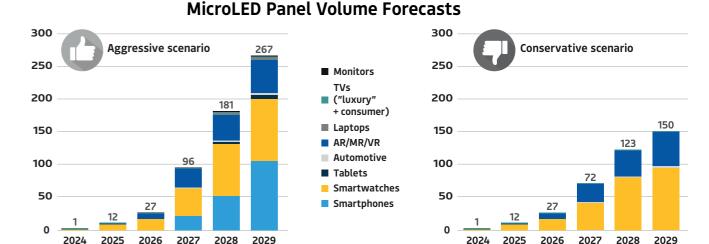

New BU Head Jakob Bollhalder answers questions on the market, Evatec scientists tell us about the fascinating world of ITO, and Dr. Eric Virey from Yole Group looks into his crystal ball to predict the future for applications of Micro and MiniLED.

# 74-89 Photonics

Find out about Evatec thin film production solutions for Augmented Reality and get Yole Group's view on the expected market development. Read how the latest manufacturing solutions can deliver the thin film quality and repeatability required for Edge Emitting Lasers to satisfy growing markets in new areas like optical communication.

LAYERS magazine is produced by Evatec AG, Hauptstrasse 1a, CH-9477 Trübbach, Switzerland. All information is correct to the best of our knowledge at the time of going to press. Product descriptions, photos and data are supplied within the brochure for general information only and may be superseded by any data contained within Evatec quotations, manuals or specifications. Evatec AG cannot be held responsible for any errors or omissions.

For any comments or queries contact allan.jaunzens@evatecnet.com. © 2023 Evatec AG. Editor-in-Chief: Allan Jaunzens. Design: Darren Stacey / Doubletake Design Ltd. (UK). Photography: Peter Fuchs / www.fuchs-peter.ch

Electronic distribution from 31st March 2023. Printed distribution from 28th April 2023.

It has continued to be an exciting time for our sector since the publication of our last LAYERS 6, with the strong investment seen in 2021 continuing through 2022. Indeed, fab equipment spending reached close to USD 110 Billion by year end 2022<sup>1</sup>. This was at a time when global supply chains had already been under pressure as a result of the COVID pandemic, and even had to ramp up to meet the new levels of demand.

As a company we have already taken a number of measures to grow both our manufacturing capacity and flexibility for the future including enlarged assembly areas. Maintaining strong long-term partnerships and working closely with both suppliers and customers is more important than ever as we look to enjoy the benefits of strong long-term industry growth all together.

While customers have been expanding their production capacity, they have also been setting us new challenges in process performance. As a result, 2022 was also an important year for product innovation at Evatec. Highlights included the launch of the new HEXAGON offering both lower R<sub>c</sub>s and higher throughputs in packaging applications and Evatec's ground breaking BAK 911 and MULTI BAK clustered evaporation solutions delivering new levels of process repeatability and lowering cost of ownership for high volume wireless applications.

I hope you will find something to inspire you in 2023 in this, our seventh addition of LAYERS. As always, we welcome your feedback about our products and services and look forward to meeting you during the year.

**Andreas Waelti CEO**

Evatec technology

world for 70 years

has been shaping the

<sup>1</sup> Numbers according to SEMI.org

Evatec expands US operations

Dan Pace and Helfried Weinzerl

**10** Evatec Europe: At the heart of Evatec's global organization Ralf Eichert

12 Becoming the Number One – All about Evatec Allan Jaunzens

Why wait? – Get the most out of your Evatec tool Mehmed Ljatifi

The company, market and technology news stories reported in this year's Corporate and Business unit chapters would not be possible without our people. They are at the heart of everything we do. My sincere thanks go out to everyone involved for their support in the production of LAYERS 7.

Allan Jaunzens

Head of Marketing and Communication

# EVATEC EXPANDS US OPERATIONS

Evatec NA Inc. recently expanded its Hillsboro, Oregon operations to become its new US headquarters. Evatec NA Inc.'s President, *Dan Pace* and Managing Director, *Helfried Weinzerl* talk about the company history and future outlook.

Congratulations to the whole US team on their success.

Andreas Waelti, Evatec CEO

# Celebrating our 20th year in the US

I have for sure made a career out of working for Swiss companies. It started with Balzers Process Systems and now for the last ~20 years with Evatec. When I was younger, I always liked the US Navy slogan... "it's not just a job it's an adventure", I can say the same for my years here. I've contributed and watched our company grow from its starting point offering sophisticated evaporation solutions in 2004. After that, we added dynamic sputter technologies in 2009, becoming a real

"Thin Film Powerhouse" after our acquisition of Oerlikon Systems. Today our offer has extended further with Atomic Layer and PECVD deposition technologies for our customers. Evatec has proven to be quite the adventure, taking me around the world to some of the most advanced fabrication facilities in our Industry. I'm proud to have contributed to our growth, and proud to be a part of this wonderful team.

As Evatec NA's President and Board Member, I'm also happy to contribute and work alongside our great team. Our presence and growth in the Pacific North West has encouraged us to open a second office, and as of 2023 our new headquarters now resides in Hillsboro, Portland, Oregon. Our East and West coast offices now work in partnership to ensure we support our customers to the fullest. The inspirational team of talented staff, including, service, office and administration personnel work professionally on all aspects of keeping business well maintained for the whole sales team. We are composed of more than 20 service specialists around North America, supporting an install base of more than 300 tools. Join us on our adventure as the Thin Film Powerhouse, as we strive to find new ways to enrich people's lives by enabling innovations; in connectivity & mobility, data processing, energy efficiency and smart sensing technologies.

#### Dan Pace

President, Evatec NA Inc.

Core Evatec NA Inc. team members at our recent 2023 Annual Team Meeting, including our 40+ year Techincal Support veterans **Gary**, (back row, 4th from right) and **Tom**, (middle row, 4th from right); our new Oregon based Operations Management, with Head of Customer Support **Francesco** (front row, 3rd from right) and Manager of Finance/HR/Admin **Tori** (middle row, 2nd from left)

# Developing the team for a growing business

# You joined Evatec North America at the end of 2019. How did it go so far?

Well, pretty much right after I joined, the pandemic hit. But, we managed well through it, thanks to our dedicated team, and our relationship with our clients. Actually, we came out stronger in many ways. Firstly, we kept on growing our local team, and started to build up a West Coast office. Secondly, we had to adapt and use new technology & communication tools to support our clients, e.g. including AR/MR technology. Finally, we had to manage and learn to co-work virtually, sometimes with colleagues who we only met for the first time after the pandemic was over. All in all, lessons learned for the future.

# How did the growth of Evatec North America manifest itself?

Throughout these 3+ years, we doubled our order intake and revenue, and we also doubled our Field Service Support team across the country. With the strong growth of our Hillsboro, OR office, we decided to make it our new US HQ, and implemented a new team of Operations & Customer Support Management staff; our former Headquarters office in Florida became our East Coast Sales & Service office.

# How would you describe the strength of your team?

Our team is very diverse in many ways. We draw strength not only from our technical know-how, but also from a multi-cultural background, as many of our team members are from all across the USA, guite a few of them with military background, others have come from other parts of the world, including myself. Several have a long history in the industry, e.g. recently we just celebrated two of our team members giving more than 40+ years service with Evatec and its predecessors (Balzers, Unaxis, Oerlikon Systems). Many others just joined us during these past 2 years. Roughly one third of our team is new, and we are constantly working to improve their skill level through cross-training, on-the-job-training, and via our new Evatec Academy at our Swiss Headquarters. We are also very proud to have female members in both operational management and field service, which is still not so common in our industry. All in all, that makes us very versatile, strong, and able to adapt to many new situations & challenges. I keep reminding my team, that success is 99% perspiration, especially for those of us in a Sales & Service organization where attention to detail and a dedicated problem-solving attitude are critical.

# What is your outlook for the upcoming years?

What excites me most about this industry is the constant drive to be on the very edge of new technology. Evatec's strategy is to be at the forefront of trailblazing industry trends, be it in the Metaverse, in e-transportation, 6G, wide-band-gap power technologies, quantum computing and semiconductor miniaturization and heterogenous integration, and so on! We strongly believe that we will grow further here in the US and globally. The US CHIPS Act will also definitely be a boost for our business here and many of our existing and potential clients are, or will be applying for funding. Therefore we need to be ready to meet their technology, process & equipment needs when they are ready. Don't get me wrong however, there will also be bumps on the road, and we can only continue to succeed with a positive attitude and working closely together with our clients.

#### **Helfried Weinzerl**

Managing Director, Evatec NA Inc.

# EVATEC EUROPE: AT THE HEART OF EVATEC'S GLOBAL ORGANIZATION

Evatec's European sales and service organization has also seen huge changes over the last 20 years. European Managing Director *Ralf Eichert* talks about how things began and where his organization is today

# You and your team have been taking care of business for Evatec since its foundation in 2004. What have been the biggest changes in that time?

Of course the transition at the start from the well established brand of Unaxis to a small unknown company was a huge change both for employees and customers. However, the initial motives of investing in and driving BAK technology forward under its own brand were well understood by customers and we were able to quickly show them positive results as a small agile company that could be flexible in its approach. Another significant milestone was the acquisition of the systems business from Oerlikon in 2014 and integration of Evatec and Oerlikon cultures to build up an exciting new future orientated team.

# How has the nature of the business changed over the last 18 years?

As a brand, we changed from an evaporation equipment supplier focused on relatively small niches within semiconductor to a true global supplier for thin film solutions across wider markets including Packaging, Optoelectronics and Photonics. Within Europe in particular

we have developed strong technology development partnerships with both academic and industrial research groups. We have invested heavily in building up the R&D facilities and process know-how to support customers at our European headquarters in Truebbach. Major European players have then gone on to roll out processes and technologies developed together with us to their manufacturing sites in Asia.

# How has your local team and the way you work changed over that time?

Of course we have grown significantly in size. Back in 2004 our sales and service organization started with around 10 people across the whole of Europe and today we are around 60 but we have also grown in breadth of knowledge too. Customer expectations for the level and speed of service available from us have also changed over the last 20 years. Stronger technical support within customer service coupled with additional new functions in our team like technical market management and application support have helped us become stronger local partners.

As our partnership with global customers has grown we have introduced key account management to improve

information flow, maintain quality and consistency in how we support them. We have strengthened internal business processes to manage the increasing complexity of our products while new software platforms have improved collaboration between ourselves, suppliers and customers making data available to everyone 24/7 at the touch of a button

# What do you see as Europe's strengths in our industry and how do you see things developing in Europe in future?

I see huge enthusiasm amongst industry colleagues in Europe with a positive "can do attitude". They are keen to develop and use their technical know-how to innovate. Our Multicultural teams are broader than ever and are well placed to help Europe lead the world in exploiting communications, healthcare and computing opportunities offered by new areas such as Quantum technology, while broader Government initiatives (e.g. US Chip Act) will offer opportunities to drive advances in manufacturing that increase capacity and lower costs.

However, I see challenges too, not just the uncertainty brought by the difficult political situation within Europe

and elsewhere right now but also be the limited human resources available to our industry at a time when we want to grow. Attracting and retaining young talented people when they have so many opportunities available to them is an ongoing task where we must all invest as an industry over the coming years.

# How do you see your local European organization developing in future?

In general I see the existing trend to expand knowledge and offer more and more customer value from our local organization continuing. As our long term cooperation with customers gets even closer and we grow and extend our markets supporting more new products and applications we will certainly need people with new technical skills too. The ongoing drive to digital transformation with access to better "data" that can be analysed more easily is also critical, whether it's in the initial design process of our products or the monitoring of their real time performance in the field. Easier access and sharing of better data will help us make better informed decisions more and more quickly. Helping our European sales and service organization be ready for the future is one of my key tasks and it's one that I love.

# Vision

Enriching people's lives by enabling innovations in connectivity & mobility, data processing, energy efficiency and smart sensing.

Our company has grown hugely since 2004 when we delivered our first BAK tools. In 2022 we were proud to deliver our 1000th tool under the Evatec brand. So here are some statistics about our company and our people today ...all sharing in one goal to help our company become the partner of choice in thin film technology.

> More than 40,000 substrates processed per year in our ECL

# **Our Business**

# **Business Units**

17 market segments in total across Advanced Packaging, Semiconductor, **Optoelectronics and Photonics**

# **Our Progress**

# Sales of CHF 270M in 2022

8 core production platforms, more than 1000 tools delivered / installed worldwide since 2004

# **Our Technology**

# **Patents**

4 core process technologies -**Evaporation, Sputter, Etch and PECVD**

# **Our Manufacturing**

# Systems assembled simultaneously

Manufacturing capacity for customer orders in three assembly halls

# **Our People**

# employees globally

>35 nationalities >15 office locations

# Our R&D

# application laboratory

Down to ISO 4 with 30 tools, 40 measurement techniques

# WHY WAIT? GET THE MOST OUT OF YOUR EVATEC TOOL

Evatec's Retrofit Manager *Mehmed Ljatifi* talks about the different benefits retrofits can bring for existing tools, how the retrofit department operates and explains why good preparation is key to success

# Tell us how you help your customers?

As a Service Department, we want to show our customers the untapped potential of their systems and how they can access that through retrofits. That could be anything from tackling obsolescence to improve uptime, to adding new hardware / process capabilities or even individual customized solutions. As Evatec's Retrofit Manager, it's my job to organize and streamline the business making sure things run smoothly for the customer. We do this with a team of system specific project managers who collaborate closely with our Product Lines Department as well as the individual business units. The focus is on our customer and their needs to make sure they get the best payback for their investment.

# Why are project managers necessary in your team?

Just like customers, every retrofit is at least slightly different even if it looks the same at first glance. We need to work with system specific project managers with a good understanding of the platform and how it has changed over the years. Retrofits can of course also be very complex. An understanding for the whole system and its configuration options needs to be mastered including the specific

customer tool and its history. We need to be sure that retrofits we make to address one aspect of performance don't adversely affect another. Only then is it possible to make sure all new elements can be integrated successfully.

# What is the difference between machine upgrades and a classic parts replacement? Where is the added value for the customer?

Of course we deal with consumables and other spare parts which can be just replaced 1:1 without further effect on the tool. Classic parts replacement is a "plug and play" story whereas a retrofit is normally much more complex. We define retrofits as where there is a change to the "bill of materials". Retrofits often need software upgrades too. Depending on the complexity of the retrofit it could often involve a much more expensive initial capital outlay, but if we talk about losing USD 1'000.every hour caused by tooldown, it is self-evident, that every retrofit that brings improvements to tool uptime can easily bring added value for the customer.

Depending on the type of retrofits we can bring a tool back to "new" to extend its working life, expand

its capabilities to run processes it couldn't before, or increase its throughput.

Bringing a customer's system fully up to date also brings other benefits too, including reducing unexpected problems. Evatec's comprehensive knowledge through its "digital twin" can also enable improved technical support at all levels.

>>>>>

Below is a simple guide to the differences between spare parts and a complete retrofit

**Definition:** A spare part is an extra piece, replaceable component (1:1), or identical to and interchangeable with the item.

- Quote provided by local organization

- In most cases the customer can replace the themselves

# **Spare Part**

#### Retrofit

**Definition:** Means a change or modification or improvement made to an equipment / assest that improves the performance, capacity and or capability of such asset.

- Definition of customer hardware / process specification

- Quote provided by Customer Service

- Installation done by Evatec

# Types of retrofits

# Tell us more about the different types of retrofits?

There are 3 different reasons why a customer should think about retrofits:

#### **Obsolete Parts**

# Reason 1

Tackling obsolescence is one of the most common reasons. For tools which have been in service for many years, the risk of long tool downs caused by important but obsolete parts breaking gets bigger. The reasons for retrofits could be the same for 2 tools but the retrofit could still differ. Let's explain it with the example of a power supply upgrade on a BAK tool. Upgrading an old EHV to the current standard EHV 510 for a customer in the US is not the same as for a customer in Europe, because an additional transformer needs to be bought by the US customer as they first need to step down from 460V to 400V. However, customers often gain additional benefits in other areas even when they retrofit for obsolecsence too. Take an obsolete server that needs to be upgraded as an example. New software will be available with many additional functions and therefore enhanced capabilities.

# **Enhanced Capabilities**

#### Reason 2

Direct requests for enhancing capabilities is another common request by customers. As component technologies improve we can often help our customers do more such as increasing process throughput by upgrading power supplies for higher coating rates. Retrofitting new improved process control technologies like the latest quartz or optical monitoring technologies for more accurate layer termination can help customers realise new processes that they couldn't achieve before, improve process repeatabilities where yields are sensitive or simply save money.

# **Customised Retrofits**

## Reason 3

Then there are also customer specific retrofits like special tooling designs unique to their own substrate geometries or process requirements. Other examples could be handling conversions from 6 to 8 inch and so on offering customers flexibility to swap between different substrate sizes easily in their daily production.

"Retrofits offer huge potential for enhanced capabilities and improving output"

# Extending working lifetimes and enhancing capability

You can find more information out at www.evatecnet.com/service/retrofits-upgrades

You can find more information out at www.youtube.com/watch?v=okXh4ast05A

# How about new ideas for retrofit services?

We are always looking at new ways of helping customers. One new area is in the field of obsolescence where its often impossible to find replacement units. With Evatec's so called "golden units service" customers can loan parts in an emergency case against a fee while their retrofit is being prepared The unit is then returned to us so we can help other customers if they run into the same situation.

# How does the retrofit ordering process work?

Prior to every retrofit our ideal process involves screening and mirroring the actual situation of the complete customer system with a tool audit executed by a Field Service Engineer. Even more helpful is a full "health check" to recognize further weaknesses and the improvement potential of the system as a whole.

Once the costs and scope of retrofit are confirmed including any tests which need to be conducted on completion of installation by the Evatec engineer an order can be placed by the customer. Our order processing groups will need to check, systemize, and confirm it before the Evatec project leaders responsible

manage the project until installation is completed on the customers system. There are many different internal stages of the project including "kick off", engineering, initial procurement, parts receipt, assembly and packing, creation of documentation including any new schematics etc, before shipping and installation is arranged often in collaboration with our local sales and service organization.

# What are the biggest challenges you face in your daily business?

The demand for thin film coating capacity has grown dramatically over the last few years. Of course, this is very good for our business as we deliver new tools but it also drives the demand for retrofits as customers look to their existing tools and how they can maximize benefits more quickly than waiting for delivery of a new tool. The COVID pandemic created huge challenges for all, but often also made the retrofit process more challenging with difficulties for access on site for surveys, tool health checks or installation work. Limited availability of electrical / electronic components and raw material as well as limited manufacturing capacities or unexpected delays on the supplier side also pushed out lead times for retrofit projects. We certainly need to avoid uncomfortable situations where we start the retrofit installation and then sudden / unexpected issues occur because the preparation with pre retrofit audit was not completed as we want. This is especially true for some of the oldest systems with unknown condition.

# Is there anything else you would like to share with our readers?

More than anything we would like to encourage and support our customers in their planning. With delivery issues at some suppliers our customers are starting to recognize the importance of advance planning of retrofits rather than waiting until the tool is down. We know our customers are all busy with day-to-day things but our job is to help them understand the cost savings they can make and budget. That helps them avoid not just a short term down time while we search for parts but avoid much more costly longer downtimes of potentially weeks because parts are obsolete and no replacement is available.

# ADVANCED PACKAGING NEWS

- 22 Chiplets and the new era of Advanced Packaging E. Jan Vardaman, TechSearch International Inc.

- Towards perfection in Advanced Packaging with the new HEXAGON Markus Frei

- Low temperature PVD deposition of low stress SiN and SiCN films for Hybrid Bonding applications

Dr. Xavier Brun, Intel; Dr. Patrick Carazzetti and Ewald Strolz, Evatec

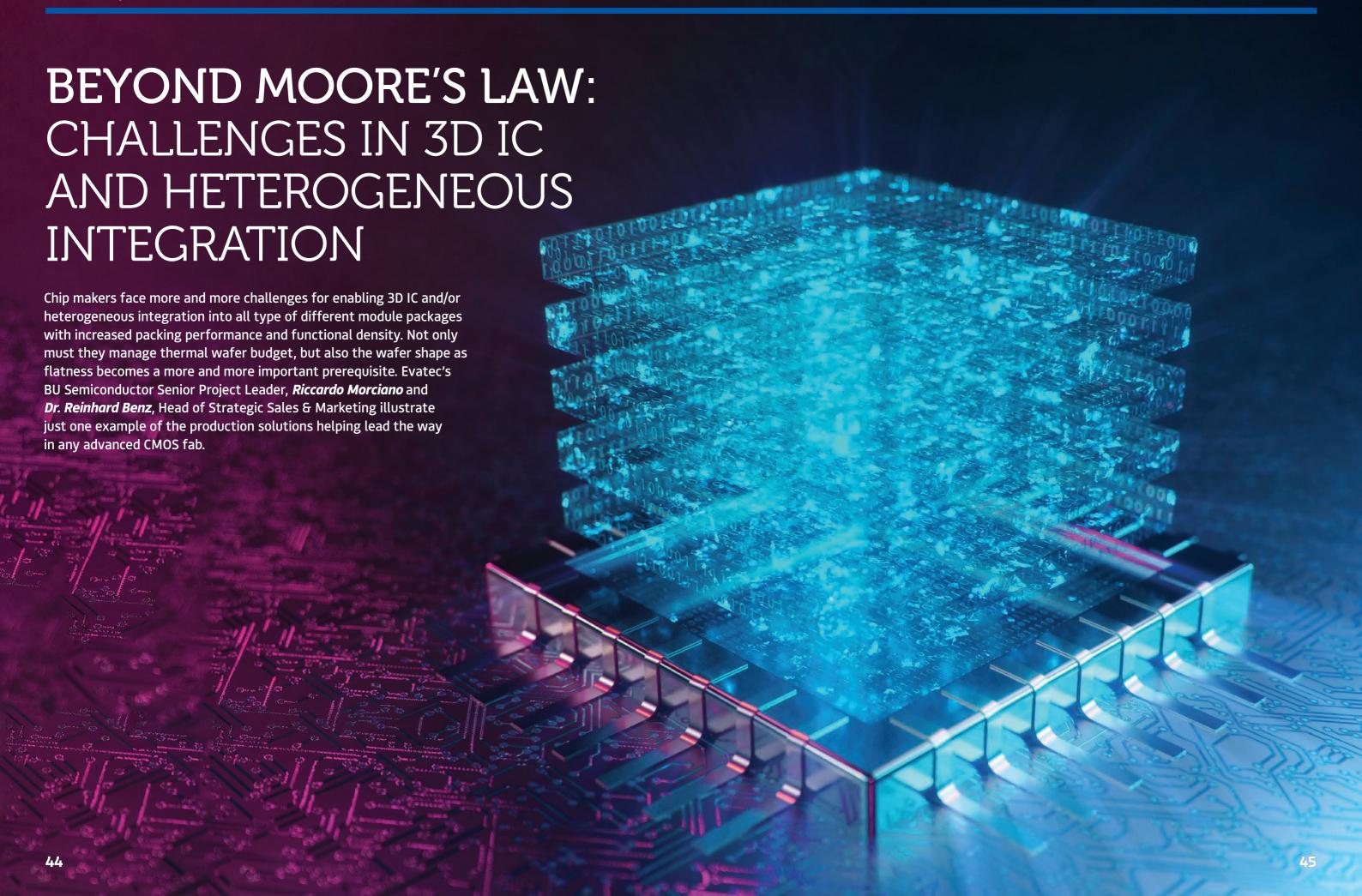

Heterogenous Integration and High Performance Computing call for new packaging designs and disruptive technologies. Chiplets are now being adopted to reduce the complexity of monolithic SOCs driving innovation in growing fields of packaging technologies, such is thermal interface materials, high density substrate technologies and fanout packaging. Panel-level packaging is finally taking off with multiple pilot lines already producing first products like application processors in high volume. Here at Evatec we continue to focus on thin film production solutions for such high-end packaging technologies. Who said Packaging is "just wrapping plastics around a semiconductor die"?... well definitely not me!

Ralph Zoberbier Head of BU Advanced Packaging

Chiplets

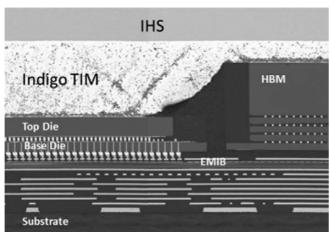

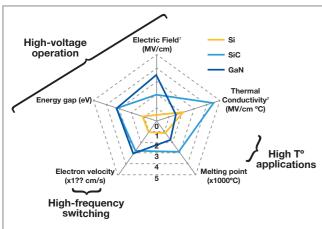

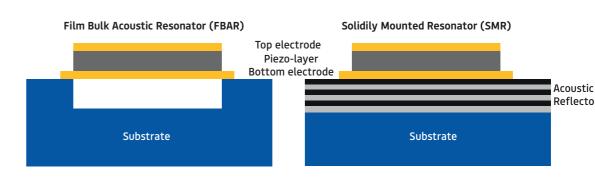

As the industry enters the new era of heterogeneous integration, advanced packaging in the form of chiplets is becoming increasingly important. An increasing number of companies are turning to chiplets to achieve the economic advantages lost with expensive monolithic scaling, ushering in a new era of smart packaging. A chiplet is not a package, but it is a new approach to system, package, and chip design. There are many package options that can be adopted and careful consideration is required to select the most appropriate options for the application. Options include the emerging 3DIC format with mircobumps or hybrid bonding, laminate substrate package, fan-out on substrate, and silicon interposer. Challenges include design, test, assembly and thermal management.

# What is a Chiplet and what are the advantages?

A chiplet is a functional circuit block and includes reusable IP blocks. A chiplet is a physically realized and tested IP with a standard or proprietary communication interface between IP blocks. A chiplet functions with other chiplets, so the design must be co-optimized and the silicon cannot be designed in isolation.

There are numerous advantages with the use of chiplets. AMD indicates that the major drivers for its adoption of chiplets include rising manufacturing cost for large die, increased cost of mask sets, increased complexity of design rules in leading-edge nodes, and architectural challenges of meeting relentless demand for increased computational power. It is also possible to have higher core counts and therefore higher performance than with a monolithic design. Cost savings at the die fabrication level can be obtained by partitioning die and only fabricating the logic functions on the most advanced nodes where needed most. Smaller die also result in higher yield per wafer, resulting in cost savings. Binning the chiplets provides an opportunity to optimize performance even further. There is a trade-off of increased cost at the packaging and assembly level. Additional costs with chiplets include increased area for interfaces, a more complex design, and often a more expensive package. However, the benefits outweigh the costs.

One of the greatest challenges is how to connect chiplet IP blocks to communicate with each other. There are many different interface options for chiplet communication. There is no single standard die-to-die interface solution in the market today. Many are proprietary, but several organizations are developing open standards. The full potential of chiplet design will not be reached until standards are established.

AMD's proprietary interface architecture is called Infinity Fabric (IF). It has been described as a superset of Hypertransport allowing for fast connectivity between different chiplets. The interface connects CPU blocks to each other and can be used to connect GPU blocks. AMD has introduced multiple generations of server and desktop products using chiplet designs [1].

| Attribute        | PVC 2T        |

|------------------|---------------|

| D2D Pitch        | 36µm          |

| Top Die Count    | 20            |

| Max Top Die Size | 41mm²         |

| Base Die Size    | 650mm²        |

| EMIB Pitch       | 55µm          |

| Core Pitch (min) | 100µm         |

| Memory (HBM)     | 8x (8Hw/BSM)  |

| Package Size     | 77.5 x 62.5mm |

| EMIB Count       | 11            |

Source: Intel

AMD INSTINCT™ MI200 OAM Series, Courtesy: AMD

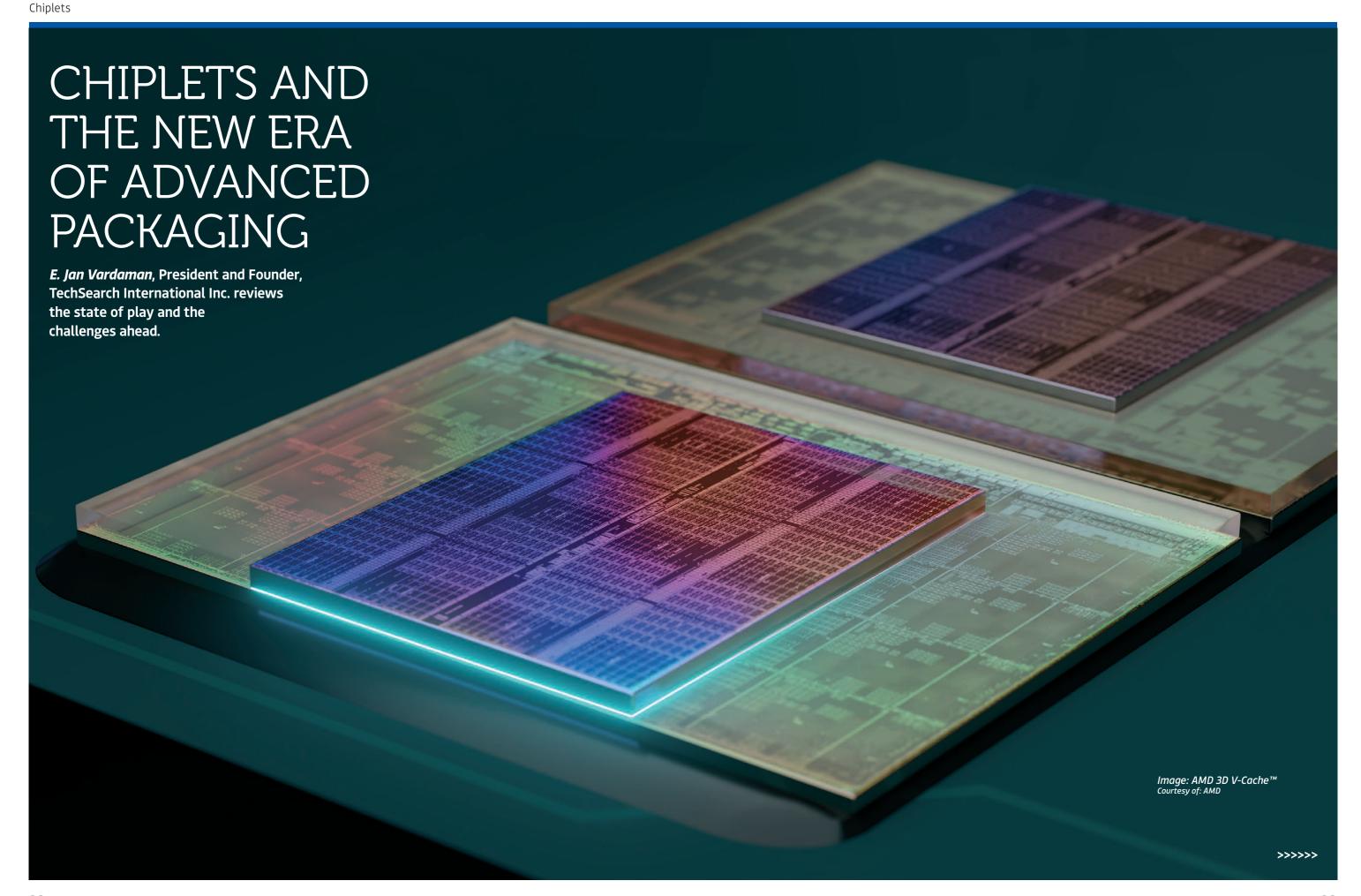

Intel has introduced Foveros technology as a chiplet solution in which a logic die fabricated on an advanced 10nm node is connected to a base die containing I/O and other functions. The base die is fabricated in a less advanced 22nm node. Intel refers to chiplets as tiles. Intel's Embedded Multi-Die Interconnect Bridge (EMIB) was developed so that the high-density connection is placed only where needed, between the die that need to communicate with chiplets such as a logic die, transceivers, and HBM. With EMIB the substrate supplier places a highdensity silicon bridge in a laminate substrate. With Intel's new GPU, Foveros tiles and HBM stacks are connected using EMIB. Intel refers to this as co-EMIB [2]. Intel's Ponte Vecchio uses a combination of Foveros and its Embedded Multi-Die Interconnect Bridge (EMIB). Two Foveros 3D configurations are in the center, plus eight HBM stacks, and two additional chips, connected with 11 silicon bridges in the EMIB. Intel will use its modular die fabric (MDF) proprietary interface for its first CPU server for datacenters.

Intel offers its AIB, a die-to-die PHY level standard royalty free. Open Domain-Specific Architecture (ODSA) has introduced Bunch of Wires (BoW). A new standard interface for chiplets, Universal Chip Interface (UCIe) is being proposed by the UCIe Consortium with members including Intel, AMD, TSMC, Microsoft, Meta, Google, Qualcomm. and ARM.

# **Chiplet Package Options**

A chiplet can be created by partitioning a die into functions and is typically attached to a silicon interposer or organic substrate today, but new options are emerging such as advanced fan-out, RDL interposer, embedded bridges, and 3D stacking. The close cooperation between all segments of the industry, EDA tool vendors, IC designers, third party IP providers, foundries, and OSATs will help drive the growth of chiplets into a wide range of applications.

#### Laminate Build-up Substrates

AMD's server, desktop, and gaming products use a laminate build-up substrate with fine features to support their chiplet designs. Intel's Foveros technology with microbump connections between the chiplets (called tiles by Intel) uses a laminate substrate to complete the package.

#### Silicon Interposers

Silicon interposer with their ultra high-density connections can support chiplet designs. Xilinx, now part of AMD, continues to use a silicon interposer for its high-end FPGA products that are fabricated in slices. Marvel will introduce a chiplet design for network switch applications using a silicon interposer.

Source: Intel

## Fan-out

Companies including ASE, Amkor, JCET, SPIL, Tongfu Microelectronics, and TSMC have introduced fan-out on substrate options for chiplets. TSMC has demonstrated a 51mm x 42mm area with five redistribution layers (RDLs) on a 110mm x 110mm substrate. A 36 $\mu$ m die-to-die I/O pitch has been demonstrated [3].

Companies have also introduced fan-out options with and embedded bridge. The embedded bridge provides the potential for a reduction in the number of RDLs and a more relaxed feature size, resulting in higher yields. AMD'S INSTINCT MI200 Series, used for machine learning, is packaged by an OSAT using Elevated Fanout Bridge (EFB) technology. GPU chiplets are connected to the HBM using a silicon bridge embedded in the RDL. The package contains two fan-out modules. Each fan-out module contains one AMD CDNATM2 die (chiplet) and four stacks of HBM2E for a total of 2 CDNATM2 die and 8 HBM2Es. The two fan-out modules are attached to the laminate substrate.

Image: AMD 3D V-Cache™ Source: AMD

# **3D IC with Hybrid Bonding**

TSMC has shown that 3D solutions such as its SoICTM using hybrid bonding to connect pads without bumps result in higher interconnect bond density. This allows the chip designer flexibility and extensibility on designing a new chip and new system device, adopting the most advanced integration technology for cost and performance advantages. Electrical resistance is lower because there is no solder bump. Lower insertion loss is also reported. High-quality signal integrity and power integrity with low RC delay and low IR drop are also reported. Energy consumption/bit is lower (as measured in pJ/bit) and thermal resistance is lower. This means less energy is required to move data around. With a fixed power envelope, less energy spent per bit means that more bits can be transferred or that the saved energy can be spent on other resources. AMD V-Cache™ using TSMC's SoIC<sup>™</sup> technology is in production for server, desktop, and gaming products. A laminate substrate is used for the package. TSMC explained the advantages of a 3D structure with hybrid bonding over a side-by-side chip layout on a silicon interposer or 3D stacking with microbumps for its SoIC™ process (see table page 23).

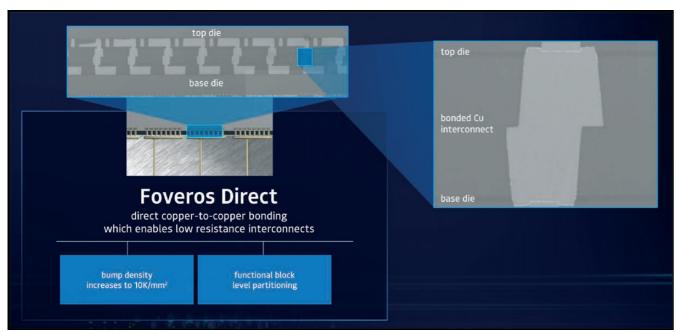

## **Intel's Foveros Direct**

Intel is developing a 3D hybrid bonding process for its Foveros technology. The focus is on sub-10µm pad pitch. In the development of its hybrid bonding process, Intel notes that there are new requirements on the bonding layer, die properties such as flatness, and tolerance to process temperatures. Design considerations include the need to consider the impact of top layer passives such as high-speed signal routes, inductors, and transforms due to increased coupling of the die (due to the proximity of the die surfaces).

SoIC™ Compared to 2.5D and Conventional 3D IC

|                   | 2.5D         | Conventional 3D IC | SolC         |

|-------------------|--------------|--------------------|--------------|

| Interconnect      | µbump + BEOL | µbump              | Bumpless     |

| Chip distance     | 100 µm       | 30 µm              | 0            |

| Bond pad pitch    | 36 µm (1.0X) | 36 μm (1.0X)       | 9 µm (0.25X) |

| Speed             | 0.01X        | 1.0X               | 11.9X        |

| Bandwidth density | 0.01X        | 1.0X               | 191.0X       |

| Power dissipation | 22.9         | 1.0X               | 0.05X        |

Source: TSMC

IBM Research is working to develop hybrid bonding for future products. 3D chiplets will be stacked using nanosheet logic die stacking. Nanosheet refers to the silicon generation that follows FinFET. The 3D stack will be mounted on a high-density laminate substrate. Samsung Electronics is developing a 3D hybrid bonding process. The focus is on logic such as CPU, GPU, and NPU plus SRAM (cache memory).

While hybrid bonding offers many advantages, there are also challenges. Samsung is focused on addressing challenges such as Cu pad surface control, cleanliness, pad alignment accuracy, bonding temperature, metrology, and developing an integrated bonding/assembly system [4].

# **Promises and Challenges**

There are tremendous advantages with the adoption of chiplets, especially using 3D hybrid bonding. 3D hybrid bonding will also offer much greater advantages than could ever be reached with monolithic scaling. The adoption of chiplets will have a similar impact on the industry as the move from peripheral chip layout to area array. The chiplet strategy is not without its challenges and associated cost. Packaging chiplets is expensive. Co-design is a must. Chiplet IP blocks must be able to communicate with each other. Standard interfaces are needed. Careful thermal analysis is important, especially with 3D stacking. Hybrid/bumpless bonding requires a clean surface for bonding and a clean environment. Particles will result in failures. New test and inspection methods are needed. These challenges are not insurmountable and an increasing number of chiplet solutions are entering the market with a growth rate of 76% expected over the next three years.

E. Jan Vardaman is president and founder of TechSearch International Inc., which has provided market research and technology trend analysis in semiconductor packaging since 1987. She is the author of numerous publications on emerging trends in semiconductor packaging and assembly. She is a senior member of IEEE EPS and is an IEEE EPS Distinguished Lecturer. She received the IMAPS GBC Partnership award in 2012, the Daniel C. Hughes, Jr. Memorial Award in 2018, the Sidney J. Stein International Award in 2019. and she is an IMAPS Fellow. She is a member of MEPTEC, SMTA, and SEMI. Before founding TechSearch International, she served on the corporate staff of Microelectronics and Computer Technology Corporation (MCC), the electronics industry's first pre-competitive research consortium.

- 1. S. Naffziger et al., "Pioneering Chiplet Technology and Design for the AMD EPYC and Ryzen Processor Families," 2021 ACM/IEEE 48th Annual International Symposium on Computer Architecture, June 2021, pp. 57-70.

- 2. E. J. Vardaman et al., "Quantifying the Impact of Heterogeneous Integration: Chiplets and SiP," TechSearch International, Inc., February 2021.

- 3. Y. Chiang et al., "InFO\_oS (Integrated Fan-Out on Substrate) Technology for Advanced Chiplet Integration," *Virtual Electronic Components and Technology Conference*, June 1 - July 4, 2021, pp. 130-135.

- 4. S.W. Yoon, "Challenges and Opportunities of Packaging FAB Near the End of Moore's Law," *IMAPS*, October 2021.

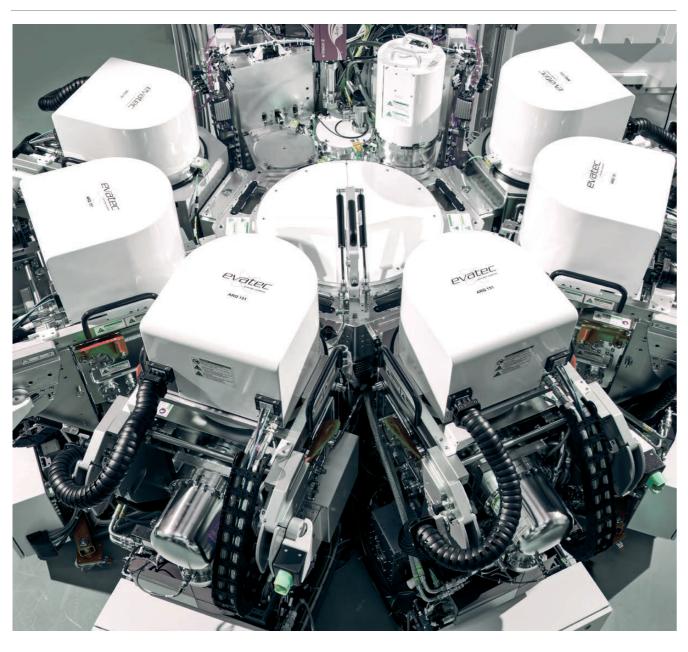

# TOWARDS PERFECTION IN ADVANCED PACKAGING WITH THE NEW HEXAGON

Building on the success of the existing system, the new HEXAGON maintains the existing strengths of proven and reliable processes, high throughput and then offers significant improvements and innovations in the areas of process capabilities, throughput, uptime, accessibility and serviceability. Product Marketing Manager *Markus Frei* tells us more.

# Why did Evatec launch a new HEXAGON?

The existing tool concept with its Indexing system was well qualified and considered by many as the benchmark in the Advanced Packaging industry for seed layer processes, but we recognised that market requirements were changing.

We wanted to deliver a platform that could address both the need for more ambitious R<sub>c</sub> requirements and the continuous push to lower Cost of Ownership (CoO). We also wanted to implement improvements based on customer feedback and provide the most robust platform in the industry.

Our goal was to bring the HEXAGON platform to the latest state of the art technology level and provide a sound solution to our customers that meets their long term process roadmap requirements.

# What are the main benefits of the new system?

The new generation tool offers a number of benefits for our customers:

- Best Rc in industry

- More uptime, lower scheduled maintenance time

- More reliability and extremely safe wafer handling

- More throughput

- More process flexibility

- More possibilities

- More accessibility

Bringing all these things together results in higher efficiency and overall CoO.

# What system aspects were essential to keep?

The handling performance and speed at the heart of the existing tool was something we very much wanted to keep. HEXAGON handles Si, EMC and Glass substrates of different sizes with ease. That also meant keeping the right degassing method.

Our second generation atmospheric high pressure degasser provides excellent degassing performance without cross contamination.

The proven indexer concept then transfers the substrate through the individual process stations with unbeatable speed to improved process modules delivering best process performance at lowest cost.

**About the author:** Markus Frei originally trained as an engineer and has over 20 years experience in vacuum and thin film technology. As product manager he gained 10 years know-how working with the unique indexing system at the heart of HEXAGON before he joined the Advanced Packaging group as Product Marketing Manager in 2021.

# What are the biggest changes?

Here are some of the biggest changes that we have made:

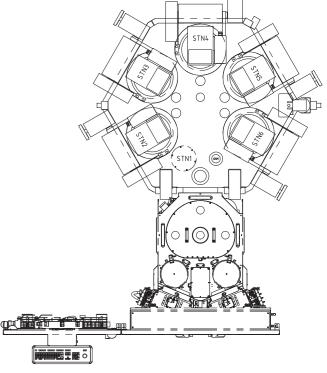

#### New Transfer Chamber (VIN6)

The new VIN6 comes with a new indexer drive. Although new to HEXAGON, it is already field proven in more than 2000 systems. The improved "on the fly" function brings even more wafer transport safety to the already existing excellent handling performance. The VIN6 accepts 5 process chambers tailored to the needs of Advanced Packaging with an optimized load lock which provides a fast wafer exchange.

# New Atmospheric Front End Module (AFEM)

We have integrated new wafer mapping and automatic home position detection that detect critical situations in the AFEM such as cross-slotted wafers, excessive wafer bow on FanOut, and double-loaded wafers. In combination with the new AWC (automatic wafer centering) function the wafer will be brought safely to the load lock.

#### Enhanced process technology

Degas: Atmospheric degas is key! Giving enough time at moderate temperature without any cross contamination is a must for processing of wafers with high organic load and especially for FanOut. Degassing at a temperature of around 120°C with a good temperature uniformity ensures even and proper degassing independent of the emissivity mix on the substrate.

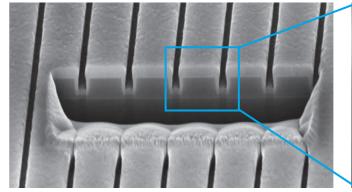

ICP: The proven SEQ 300 etch cathode offers improved uniformity with a newly designed chuck. Evatec's patented insitu pasting solution is also available as an option. Adding in a new etch chamber design and the longest "Kit life" in the industry results in the best etch performance ever.

**PVD:** Our well known ARQ 310 provides efficient deposition. Using only 400mm diameter long-life targets together with our uniformity compensation over target life we reach a new benchmark for target lifetimes but also for CoO.

## New services system

The media distribution system is designed into the base pedestal, resulting in easy installation, good access, and easy maintenance.

#### New control system

A new control system comes with the proven Siemens TIA portal and state of the art GUI giving you direct access to your hardware components like drivers for maintenance and service. No additional software or devices are needed.

For those already familiar with Evatec's latest CLUSTERLINE® generation which uses the same software platform, minimum cross training will be required for operation, maintenance and service. New features eliminate or reduces complex tasks like teaching and calibration and other improvements make the system easier to work with.

# Unified platform concept

The approach taken in the newly designed HEXAGON and CLUSTERLINE® platforms brings benefits for long term field support too. Modular and standardized design leads to fewer individual parts, the smart modules use distributed I/O functions, and a powerful Profinet bus simplifies the system, increasing uptime and productivity. Optimised architecture of the system results in faster manufacturing times and reduced ramp up-time to production. Footprint of the system is reduced taking up less costly cleanroom space and the system is designed to meet the newest ISO 14001 environmental standards, conserving water usage and energy.

#### Welcome to the new HEXAGON

We are excited to see the performance of our system with an even safer level of wafer handling to protect the high value of our customers' wafers.

Combined with the benefits from higher productivity, higher throughput, reduced maintenance time and easier support during its working life, the new HEXAGON system really does set new standards for Advanced Packaging applications.

# The new HEXAGON improvements at a glance

- New direct servo drive system

- New standardized 3 wide AFEM

- New control system

- Improved throughput

- Insitu pasting available

- Improved etch uniformity

- Modified Atmospheric Batch Degasser

- Optimized Loadlock

- Incorporating automatic wafer centering, reduced volume

- New process modules

- Higher pumping speed

- Improved system service and maintainability

HEXAGON

0

Find out more information at evatecnet.com/products/hexagon

# **Facts and figures**

2000

The new VIN6 Transfer Chamber comes with a new indexer drive already field proven in more than 2000 systems.

100

Enjoy throughputs of >100 wafers per hour according to process.

Configure up to 5 process modules for etch and deposition processes.

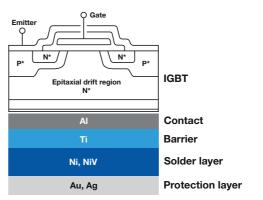

# LOW TEMPERATURE PVD DEPOSITION OF LOW STRESS SIN AND SICN FILMS FOR HYBRID BONDING APPLICATIONS

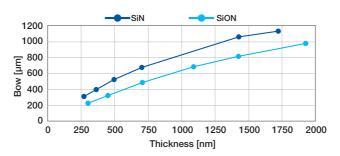

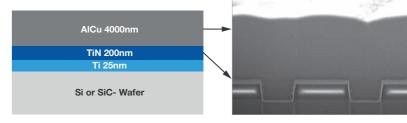

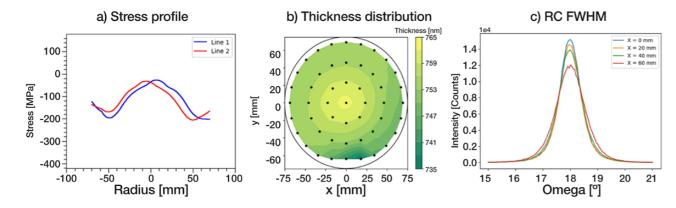

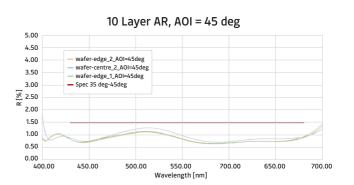

Intel's **Dr. Xavier Brun**, and Evatec's **Dr. Patrick Carazzetti** and **Ewald Strolz** investigate the feasibility of high quality low stress SiN and SiCN film deposition on Evatec's CLUSTERLINE® at low temperatures without adversly affecting tool productivity. Results confirm the possibility of achieving good uniformities (<3% 1 $\sigma$ ) for up to 2.0 $\mu$ m films, and optimization of SiN film stress (100MPa) independent of film thickness.

#### Introduction

As transistors' density grows with each new Silicon node, the package technology needs to scale accordingly. New challenges in packaging arise as the pitch of the first-levelinterconnects (FLI) shrinks below what can be achieved with solder joints. Hybrid bonding, including dielectric bonding plus direct Cu-Cu bonding, is a promising solution, but faces significant integration challenges due to the stringent requirements to enable a high yield bonding process for dielectric and Cu interfaces while maintaining low processing temperatures to ensure package integrity. Many studies have demonstrated the benefit of silicon carbonitride (SiCN) dielectric compared to silicon oxide (SiO<sub>2</sub>) for decreasing the bonding temperature, specifically reducing the annealing temperature below or equal to 250°C. Unfortunately, these studies have leveraged plasma enhanced chemical vapor deposition (PECVD) which requires high deposition temperature (i.e., 370°C) and precursors. In addition, these films necessitate prebonding densification above deposition temperature to prevent voiding at the bonding interface [1-3]. PVD was recently reported to be a superior alternative method for silicon nitride (SiN) dielectric deposition for bonding applications with low deposition temperature, not requiring densification pre-bonding, and achieving comparable bond strength with low post-bonding annealing temperature [4].

Significant work on PECVD SiN and SiCN deposition of thin films on silicon substrate semiconductor device has been reported in the literature [5], of particular interest

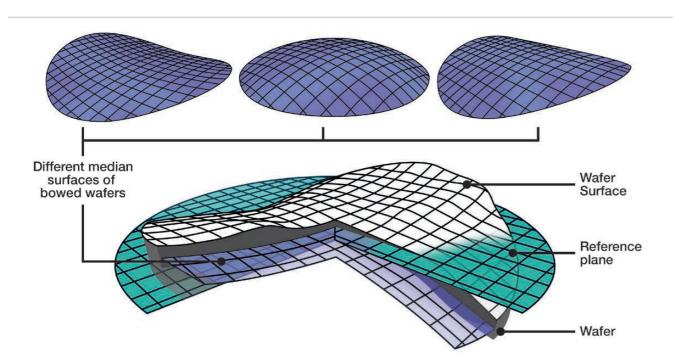

[6] reported the impact of substrate temperature for SiCN PECVD on film growth and composition. High substrate temperatures (>400°C) are needed to ensure mass transport mechanism for film deposition in addition to limiting the oxygen content in the film [6]. However, limited work has been done on the use of PVD for the dielectric film deposition process for advanced packaging applications, particularly looking at ensuring the low temperatures required for device integrity (<250°C). To this end, a set of low temperature PVD depositions of SiN and SiCN thin films on p-type (100) Silicon substrates is presented here. The deposition temperature as a function of the deposition time is characterized. In order to provide insights of handling flexibility, two hardware configurations have been tested depending on if contact on non-deposition side of the substrate is allowed. In both cases, an optimized process is presented to minimize the substrate temperature. In order to mitigate the impact of stress induced warpage at wafer level and its impact on downstream applications, the deposition process was optimized to target minimum film stress and make the stress essentially independent of the film thickness. Therefore, the film stress is characterized as a function of the film thickness. To comprehend a wide range of packaging applications, the low temperature deposition of SiN on epoxy mold compound (EMC) is also presented. The quality and hermiticity of the deposited films have been assessed on both inorganic and organic substrates with accelerated temperature and moisture bake experiments.

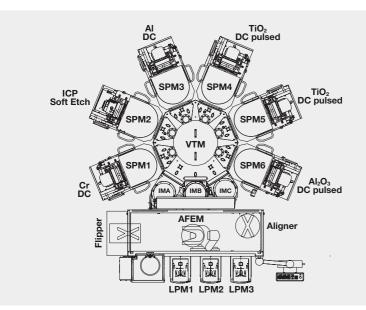

This study presents a comparison of SiN and SiCN thin films sputtered on a high-volume manufacturing CLUSTERLINE® PVD platform. Of particular interest is the limitation of the deposition temperature without adversely impacting tool productivity (e.g., the run-rate). The impact of the film thickness on stress and warpage is reported. Although this study focuses on blanket films, fundamentals are presented to define the best integration for packaging applications such as hybrid bond dielectric preparation for FLI bonding, or direct bond dielectric preparation to combine heterogenous materials (e.g., integrating a Si passive interposer on backside of an exposed die package for improved thermal performance).

# **Experimental Method**

# Film deposition and characterization

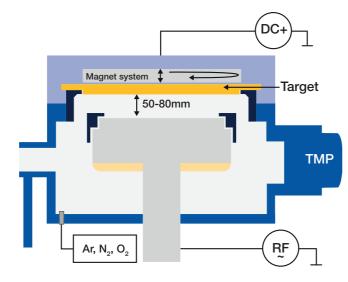

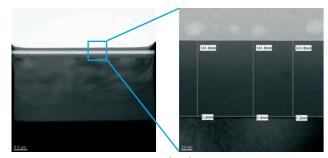

Magnetron sputtering is a well-established PVD technology in microelectronics manufacturing and advanced packaging for the deposition of metal and dielectric films. The main benefits of magnetron sputtering include high deposition rates, excellent thickness uniformity, tight defect control and low deposition temperatures compared to CVD and PECVD counterparts. In this work, amorphous films of silicon nitride (a-SixNy) and silicon carbonitride (a-SiCxNy) were deposited on bare silicon substrates by DC magnetron sputtering in a mixed atmosphere of nitrogen and argon. The main hardware features of the process modules, as well as the key process conditions are summarized in Table 1. A polycrystalline Si target with 400mm diameter was used to sputter SiN in a CLUSTERELINE® 300 high-volume manufacturing tool configured for 300mm wafer sizes. The deposition conditions of the SiN best-known method (BKM), such as power density, N<sub>2</sub>/Ar gas ratio and process pressure are reported in Table 1. Two important tuning knobs have been identified to reduce the stress of SiN films. These are the use of DC power in pulsed mode, in combination with the increased process pressure obtained by pump throttling. The SiCN films were prepared on a CLUSTERLINE® 200 platform configured for 200mm wafer sizes. This tool was equipped with a 300mm diameter powder pressed SiC target, with a 1:1 silicon/carbon ratio. The process conditions of the established SiCN BKM are also reported in Table 1.

Both of the CLUSTERLINE® platforms used are both multi-chamber PVD tools with up to six process modules clustered around a central vacuum transport section. This configuration allows execution of a sequence of processes in different modules without breaking vacuum. The CLUSTERLINE® 300 configured for BSM processes, uses recessed chucks to prevent direct contact of the device side of the wafer with the pedestal surface. Only the wafer perimeter rests on a metal supporting ring located around the chuck top. The additional requirement for full face deposition in BSM applications forbids the use of any

mechanical fixation of the substrate edge. Therefore, the substrate can only dissipate the heat (generated by the film growth) through radiation. To favor such heat dissipation so that the increase of temperature during deposition is limited, a simple approach was followed: alternating deposition steps with cooling steps. The implications of such "split process" on the wafer temperature and the corresponding run-rate will be discussed in Section III. Contrary to the CLUSTERLINE® 300, the CLUSTERLINE® 200 was not bound by a BSM hardware configuration. Instead, the PVD module used in this work was equipped with a clamping setup, that mechanically fixates the wafer edge by the mass of the clamping mask. As a result, the entire wafer surface is in contact with the water-cooled pedestal. Moreover, Ar gas flows beneath the substrate through a dedicated inlet at the center of the chuck and it is distributed over the entire wafer surface by a network of grooves thereby promoting efficient cooling by

In advanced packaging applications, the common practice to pre-treat a substrate prior film deposition consists of a sequence of degas and soft-etching processes [7]. Degas is applied to eliminate surface moisture from the organic films and substrates by heating the wafer typically up to 120-150°C. The subsequent soft-etching takes place in a dedicated Inductively Coupled Plasma (ICP) Etch module. Here, the bombardment of the substrate by low-energy Ar plasma effectively eliminates surface contamination and native oxides, thereby enhancing adhesion of the subsequent PVD film.

| Hardware<br>and Process          | Film / PVD System                                            |                                                                           |  |

|----------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------|--|

| Conditions                       | Sin /<br>CLUSTERLINE® 300                                    | SiCN /<br>CLUSTERLINE® 200                                                |  |

| Target                           | Si polycrystalline<br>(disc Φ=400mm)                         | SiC powder pressed<br>(1:1 ratio, disc<br>Φ=300mm)                        |  |

| Power source                     | Pulsed DC<br>(frequency=350kHz;<br>pulse-off<br>time=1100ns) | Continuous DC                                                             |  |

| Power density<br>[W/cm²]         | 6.37                                                         | 4.95                                                                      |  |

| Gas ratio N <sub>2</sub> /Ar [-] | 1.0                                                          | 1.2                                                                       |  |

| Sputtering pressure [mbar]       | 1.3e <sup>-2</sup> (pump<br>throttled)                       | 9.7e <sup>-4</sup>                                                        |  |

| Pedestal type                    | Clampless, recessed<br>chuck top, PCW<br>cooled pedestal     | Clamped, flat chuck<br>top with back-gas<br>inlet, PCW cooled<br>pedestal |  |

| Pre-treatment process            | Radiation degas<br>(load-lock) and<br>ICP-Etch               | ICP-Etch                                                                  |  |

Table 1: Hardware configuration and process conditions used to sputter deposit SiN and SiCN films.

>>>>>

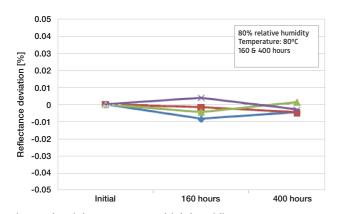

#### Low temperature SiN reliability assessment

In this section, the focus is on reliability of the low temperature deposited films. SiN films were deposited on both inorganic materials, i.e. p-type (100) Silicon substrate, and organic materials, such as EMC on a Si substrate, to comprehend a wide range of packaging applications. All the samples were processed using the same low temperature process described above on the 300mm tool. To improve the adhesion to the organic material interface, this study includes understanding the impact of an ICP-etch step pre-deposition. To envelope a range of mold materials available, two different mold compounds were compared side by side. As shown in Table 2, liquid and granular EMC have different mechanical properties particularly Young's Modulus and Coefficient of Thermal Expansion (CTE).

|           | Sample                  |                       |              | nanical<br>perties |

|-----------|-------------------------|-----------------------|--------------|--------------------|

|           | Stack                   | Interface<br>Material | CTE<br>[ppm] | E<br>[GPa]         |

| Inorganic | 1.5µm SiN<br>775µm Si   | Silicon               | 2.3          | 170                |

| 0         | 1.5µm SiN<br>100µm Mold | Granular<br>EMC       | 5.0          | 20                 |

| Urganic   | Organic 775µm Si        | Liquid<br>EMC         | 16.0         | 9                  |

Table 2: Material properties - SiN reliability experiments

After deposition, standard diamond dicing was used to singulate the wafers into samples that were then submitted to Temperature/Humidity plus preconditioning (JEDEC standard J-STD-020 [8]) and extreme preconditioning for margin assessment and HTSL/Bake (JESD22-A103 [9]) to accelerate SiN de-lamination and dielectric cracking failure modes. The cracking in SiN results from moisture assisted crack growth propagation. Macroscopic and microscopic inspections were performed to detect the presence of defects such as SiN cracking, flaking, fringing, etc., both post singulation and post temperature/humidity exposure.

## **Results and discussion**

#### Films performance summary

In this experimental study, various SiN and SiCN films with thickness ranging from 100nm up to 2.0µm were sputtered on bare silicon wafers and were characterized without performing any densification or annealing. Spectroscopic ellipsometry (Woollam M-2000) was used to measure film thickness, refractive index (n) and extinction coefficient (k). In-wafer statistical data was collected using a 49-points circular pattern with 6.0mm edge exclusion. The film

uniformity is an important metric to characterize the quality of a deposition process. The uniformity criteria adopted here is " $1\sigma$ ", which is defined as standard deviation of the thickness distribution divided by the average. The film density is calculated based on the mass difference of the wafer pre- versus post-deposition. Table 3 summarizes data measured on 2.0µm-thick films of SiN and SiCN. The obtained  $1\sigma$  uniformities are below 3% for both films. These values can be considered satisfactory and show that the PVD processes developed are suitable for depositing high-quality films at least up to 2.0µm with deposition rates in excess of 20.0Å/sec. We measured a SiN refractive index of 2.11. This can be compared to published n values ranging from 3.18 to 2.1 with N/Si ratio increasing from 0.31 to 1.5 [10]. The measured density of the 2.0µm SiN film is 2.7 +0.05 g/cm<sup>3</sup>. This value matches well with published data of 2.8 g/cm<sup>3</sup> for a film with N/Si ratio of 1.1 [11] and 2.28 to 2.97 g/cm<sup>3</sup> depending on the deposition pressure [12]. The refractive index of the SiCN film is 2.29 and the corresponding density is 3.5 +0.5 g/cm<sup>3</sup>. Published data show a direct relationship between increase in the nitrogen content in the film and the concomitant increase of both density and refractive index. Inoue et al. [3] reported a refractive index of 1.95 and a corresponding density of 1.98 g/cm<sup>3</sup>.

|                                   | Film / Substrate               |                                               |  |

|-----------------------------------|--------------------------------|-----------------------------------------------|--|

| Performance                       | SiN / 300mm<br>wafer           | SiN / 200mm<br>wafer                          |  |

| Deposition rate<br>[Å/sec]        | 20.71                          | 23.68                                         |  |

| Thickness<br>uniformity, 1σ [%]   | 2.97                           | 1.62                                          |  |

| Refractive index, n<br>@633nm [-] | 2.11<br>(3.18-2.1 in [10])     | 2.29<br>(1.95 in [3], and<br>2.1-2.3 in [13]) |  |

| Density as-<br>sputtered [g/cm³]  | 2.7 ± 0.05<br>(2.8 in [11,12]) | 3.5 ± 0.5<br>(1.98 in [3])                    |  |

Table 3: Properties of 2.0µm SiN and SiCN films

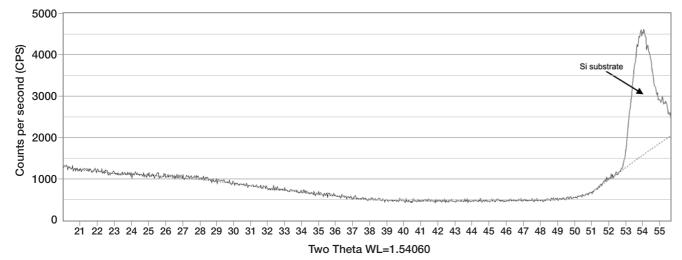

#### Elastic recoil detection analysis (ERDA)

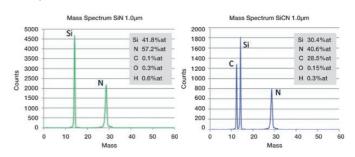

ERD analysis uses high-energy heavy ion beam to determine the elemental depth concentration profiles in thin films [14]. In this work, the analysis was performed on selected samples of 1.0µm SiN and 1.0µm SiCN by 13 MeV 127I Heavy Ion ERDA. The elemental composition was retrieved from the bulk of the film at a depth of about ~30-150nm so that the surface contamination is not considered. ERD spectra of SiN and SiCN films are displayed in Figure 1. The empirical stoichiometry formulas reported in Table 4 were established based on the elemental composition normalized to Si. In the case of SiN, a normalization factor of 3 was used; whereas, in the case of SiCN the normalization factor was 1.

The ratio of Si to N in the silicon nitride film is 3 to 4.1, indicating that a nearly stoichiometric Si3N4 is formed. The other elements in the measured mass spectrum: C(<0.1%at), H(<0.6%at) and O(<0.3%at) are present as impurities. Published research shows that the N/Si ratio can be tuned between 0.56 (under-stoichiometric) and 1.33 (stoichiometric) depending on the N2/Ar ratio in the process atmosphere [15]. The ratio of Si to C in the SiCN film is 1 to 0.99, which validates the nominal composition of the target. Beside the target elements and nitrogen, experimental data show a very minor content of H (<0.3%at) and O (<0.15%at). In the linear scale spectrum such low content of H and O is not visible. The composition of SiCN produced in this work is richer in nitrogen and it is substantially hydrogen-free compared to the published data [3].

| Film     | Empirical formula |       |      |       |       |

|----------|-------------------|-------|------|-------|-------|

|          | Si                | С     | N    | Н     | O     |

| SiN      | 3                 | 0.006 | 4.1  | 0.024 | 0.041 |

| SiCN     | 1                 | 0.99  | 1.40 | 0.01  | 0.005 |

| SiCN [3] | 1                 | 0.79  | 0.75 | 0.62  | 0.003 |

Table 4: Empirical stoichiometry formula of sputter deposited SiN and SiCN films derived from ERD analysis

# Wafer temperature and stress vs. film thickness

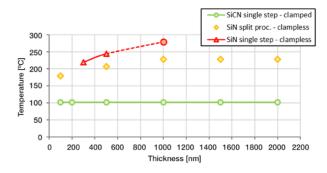

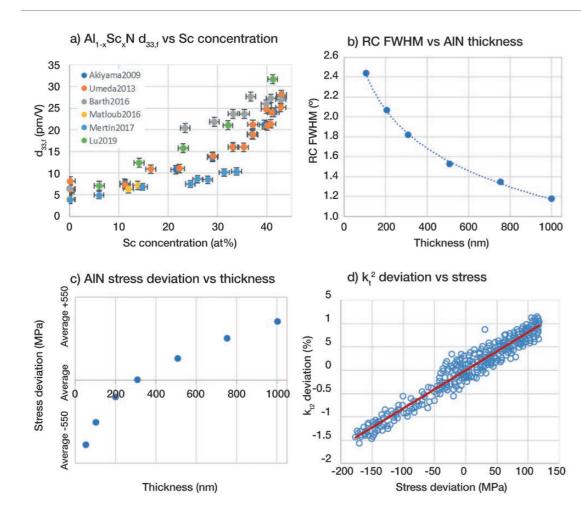

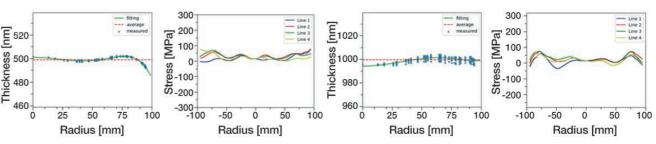

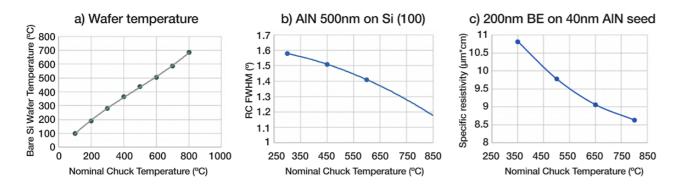

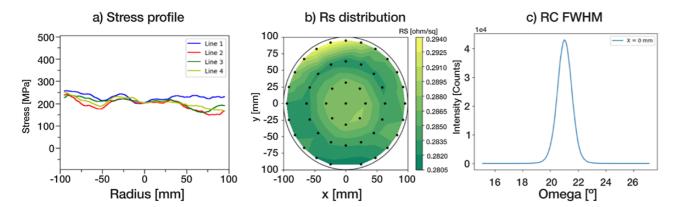

The maximum temperature of the wafer during deposition was measured using thermal labels (Celsistrip® Spirig – Switzerland). These labels use a scale of markers reacting at a progressively higher temperature in steps of 5-6°C, which represents the measurement resolution. Each marker turns to black when triggered, thereby indicating the peak temperature reached during process. In our tests, the thermal label was placed on the deposition side at the center of each monitor wafer. Figure 2 compares the process temperature versus the film thickness for SiN films produced on CLUSTERLINE® 300 (split deposition process), and SiCN films produced on CLUSTERLINE® 200 (single step deposition process).

The strategy of splitting the deposition process alternates deposition steps of 100nm (equivalent to a process time of 47.0sec) followed by a cooling step of 60sec. Five different films with thickness ranging from 100nm up to 2.0µm were deposited in this process regime. Prior to PVD, each monitor wafer was pre-treated with degas and ICP-etch, which resulted in a peak temperature of ~150°C. The peak temperature post PVD shows an increase to ~180°C for the 100nm SiN film, up to ~207°C for the 500nm film and then a stabilization to ~228°C for all other thicker films (\* markers in Figure 2). This behavior indicates the effectiveness of the deposition/cooling regime adopted to stabilize the peak temperature. As a comparison, SiN deposition of 300nm, 500nm run in a single step without cooling reach ~40-50°C higher temperature (▲ markers in Figure 2), and the 1.0µm process exceeded the upper range of 260°C.

SiCN processes run on CLUSTERLINE® 200 indicate a stable temperature of ~100°C, independently from the film thickness (• markers in Figure 2). In fact, it was shown that 100°C substrate temperature was reached already during the ICP-etch prior deposition. This highlights the effectiveness of the hardware setup combining mechanical wafer clamping and active back-gas cooling.

Figure 2: Peak wafer temperature corresponding to SiN and SiCN films of various thickness processed either in single deposition step, or split process, respectively.

An additional set of wafers processed with the same condition was used to characterize the residual film stress. The in-plane stress was measured by recording the change of the curvature radius of the substrate induced by the deposition process [16]. The wafer curvature and bow were measured optically with a stress analyzer Tencor FLX-3300-T. The well-known Stoney's formula was used to relate the measured substrate curvature to the residual film

$$\sigma = \frac{E_s}{6(1 - \vartheta_s)} \cdot \frac{t_s^2}{t_f} \left[ \frac{1}{R_1} - \frac{1}{R_0} \right]$$

Where Es/ $(1-v_s)$  is the biaxial Young's modulus of the substrate (180.5 GPa for (100) oriented Si wafers), ts and tf represent the thickness of substrate and film, respectively. R0 and R1 are the curvature radii before and after deposition. The measured stress as a function of the

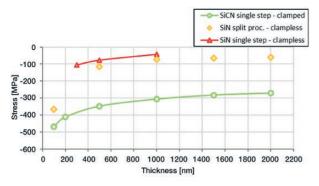

film thickness are displayed in Figure 3. Both SiN and SiCN films exhibit a compressive stress level, which becomes more moderate as the thickness increases. Particularly, a stabilization is observed when the film thicknesses exceeds 1.0µm. In the case of SiN, a plateau is reached at -65 +5MPa, whereas the stress of SiCN films levels off around -280 +20MPa. Residual compressive stress level means that the deposition process has produced a dense and compressed film, which tends to expand in order to relax its internal energy. In this case, the film expansion exerted on the substrate results in a convex warpage [17]. In the worst-case scenario, a highly compressive stress distribution can lead to catastrophic failure mechanisms, such as film buckling, blistering or peeling off. However, the moderate compressive stress of SiN films obtained in this work should not represent concerns of the film integrity, or subsequent integration and device reliability issues. The minimization of SiCN stress can also be investigated by using tuning knobs, such as DC sputtering in pulsed mode and pressure modulation, similarly to SiN. This will be addressed in future work.

Figure 3: Film stress a function of the thickness for single step SiCN deposition process, and single step versus split process

#### Run-rate vs. film thickness

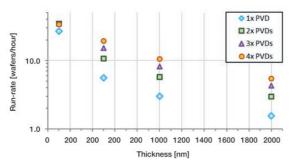

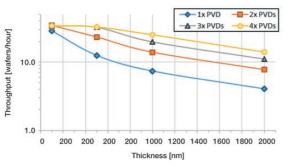

In order to keep a viable tool productivity, especially when processing thick films with stringent temperature requirements, it may be necessary to have more than one deposition chambers. This section provides some guidelines to establish the suitable tool configuration based on the required film thickness and the run-rate goal. The run-rate defines the tool output in terms of number of wafers per hour processed from job start to end. Different scenarios have been considered and executed on the HVM platform equipped with one ICP-Etch and up to four PVD chambers. The run-rate figures are reported in Figure 4.a (split deposition process like SiN) and Figure 4.b (single-step deposition).

Figure 4: Run-rate vs. film thickness and number of PVD chambers: (a) SiN split deposition process with cooling steps, and (b) SiCN single step deposition process

#### **Stress Test Results**

Stress test experiments were performed with low temperature SiN layer singulated samples on two types of EMC and the Bare Si. For the EMC samples, ICP etch was studied to understand its impact on the SiN to EMC adhesion. For each leg, a total of 6 units were used. Table 5 summarizes the reliability results for all the samples. For the silicon samples, no gross delamination was observed on all the conditions. This is because the CTE mismatch between Si and SiN is lower, which leads to lower shear stress at the interface as the temperature changes. Thus, the risk for the interfacial delamination is lower than the one for the organic samples.

|           | Sampl        |              | Reliability results [# units with delamination/total units |                                                          |                  |

|-----------|--------------|--------------|------------------------------------------------------------|----------------------------------------------------------|------------------|

| Type      | Mold<br>type | Pre-<br>Etch | 168hrs<br>60°C /<br>60%<br>RH +10x<br>reflow<br>260°C      | 216hrs<br>30°C /<br>60%<br>RH<br>+ 3x<br>reflow<br>260°C | 1000hrs<br>150°C |

| Inorganic | None         | No           | 0/6                                                        | 0/6                                                      | 0/6              |

|           | Granular     | No           | 6/6                                                        | 6/6                                                      | 0/6              |

| Organic   | Granular     | Yes          | 0/6                                                        | 0/6                                                      | 0/6              |

| Organic   | Liquid       | No           | 0/6                                                        | 2/6                                                      | 0/6              |

|           | Liquid       | Yes          | 0/6                                                        | 0/6                                                      | 0/6              |

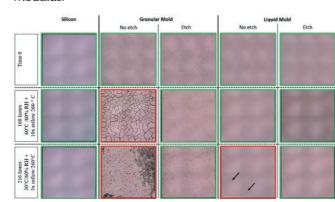

Table 5: Low temperature SiN reliability results

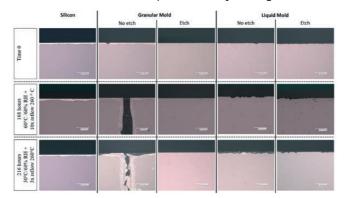

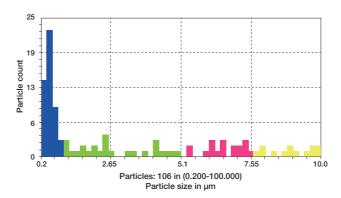

All the units were also inspected for SiN cracking optically. Only the units with no etch showed SiN cracking for both granular mold and liquid mold, with the latter being less severe (Figure 5). Although Liquid mold having higher CTE mismatch shows better performance than granular, this could be due to its much lower young's modulus and more significant stress relaxation for liquid mold material [18]. Blade dicing impact on SiN was also analyzed side by side for all the samples at time 0 and post reliability test. Si substrate and all organic non-etched samples showed fringes representing SiN delamination at the edge of the sample in Figure 6. Note that no delamination extension was observed post reliability on the Si substrates. A clear benefit was observed with the addition of the etch process for both organic materials. In addition, it was observed that granular mold singulation chipping performance was qualitatively better than the liquid mold material, which could be explained due to its higher hardness or young's modulus.

Figure 5: Low temperature SiN surface macro inspection (3x diopter) on organic and inorganic substrates with and without etch at time 0 and post reliability testing

Figure 6: Low temperature SiN surface and singulated edge micro inspection (20x microscope) on organic and inorganic substrates with and without etch at time 0 and post

To further investigate the low temperature SiN delamination mechanism, additional inspection was carried for the granular EMC post reliability. Massive cracks in nitride are observed throughout the sample at 20x (Figure 7a). By looking at higher magnification, areas of flaked nitride were observed along with exposed mold (Figure 7b). Exposed

mold showed areas of small filler pull out with intact large fillers (Figure 7c). Bottom of flaked nitride was inspected (Figure 7d) and revealed presence of small fillers indicating cohesive failure within the mold. Energy dispersive spectroscopy (EDS) confirmed the presence of mold fillers at the bottom of flaked nitride (Figure 7e).

#### Granular Mold (No etch)

Figure 7: Low temperature SiN surface inspection (SEM) on granular EMC substrate without etch post reliability. a) Gross SiN cracking observed at 20x, b) Mold exposed and SiN flaking observed at 250x, c) Exposed Mold area without SiN (delaminated area) at 10kx, d) Bottom of SiN (delaminated area) at 10kx, e) EDS analysis on bottom of SiN confirming mold filler pull out

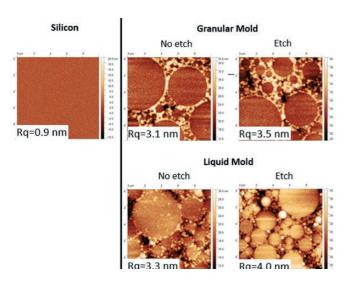

Although, within mold cohesive failure was observed for granular mold, it is still important to understand the influence of etching. As mentioned earlier, soft etching is generally performed to clean surfaces before deposition. This would not explain the difference in performances between the liquid and granular mold observed in the reliability tests. Therefore, additional characterization with atomic force was performed demonstrating the etch impact on surface roughness. In all cases, etch increased the roughness of the mold compound, therefore, increased the contact area with the deposited nitride. As a result, it provided better mechanical interlocking of the SiN film with the organic material (Figure 8). Interestingly, unetched liquid sample showed higher roughness compared to granular mold that may explain the reliability difference.

>>>>>

Figure 8: Low temperature SiN surface roughness measurement (AFM) on organic and inorganic substrates with and without etch at time 0.

#### Conclusion

A low temperature PVD dielectric deposition process has been demonstrated both for SiN and SiCN thin films. This helps Hybrid bonding integration and ensure package integrity by lowering the deposition process temperature. PVD of SiN and SiCN films with good uniformity for up to 2.0µm film thickness was demonstrated. Residual stress was characterized to understand its impact on the wafer warpage. For both dielectrics, above a minimum film thickness, the stress becomes almost independent of the film thickness. The SiN process was optimized to near zero stress (~50MPa compressive) on Silicon substrate, indicating a minimized impact on wafer warpage. The criticality of the substrate cooling was observed. Two different deposition approaches were presented: one by splitting the process with deposition and cooling cycles; the other by leveraging an improved cooling path for the substrate. Both approaches showed effective substrate temperature control, with the later had less impact on the run-rate. Compared to PECVD films, which use precursor gases, PVD films are free of impurities and do not require any densification (annealing). Industry usually requires above deposition temperature densification to prevent voiding at the bond interface. The PVD deposited SiN composition showed low Hydrogen content. The SiCN PVD obtained was Nitrogen rich compared to PECVD films, its chemical composition on Bonding performance will be investigated in the future.

Reliability of SiN was studied on both inorganic and organic interfaces. Films' quality and hermiticity were assessed with accelerated temperature and moisture bake experiments. Adding ICP-etch on EMC before SiN deposition improved film adhesion with an increased surface roughness and samples survived all the stress conditions, while un-etched samples exhibited SiN cracking and delamination.

# Acknowledgement

The authors wish to acknowledge Joel Fischer and Nico Lipp at Evatec for valuable support, and Max Döbeli at ETHZ for ERD analysis. In addition, the contributions of multiple stakeholders within Intel FA and reliability team, Shashank Kaira for the films inspections, Mohit Khurana for AFM characterization, Sarah Wozny and Alan Johnson for their discussions on film reliability.

#### References

- [1] S. Kim, L. Peng, A. Miller, G. Beyer, E. Beyne and C. Lee, "Permanent wafer bonding in the low temperature by using various plasma enhanced chemical vapour deposition dielectrics", 2015 International 3D Systems Integration Conference (3DIC), 2015, pp. TS7.2.1-TS7.2.4.

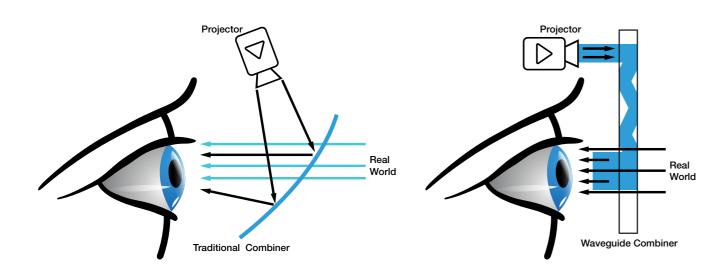

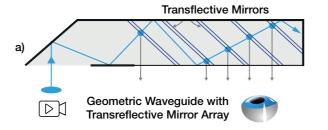

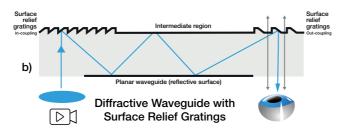

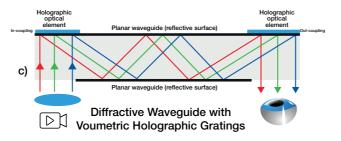

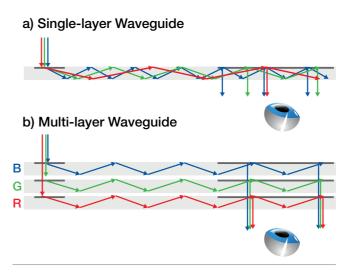

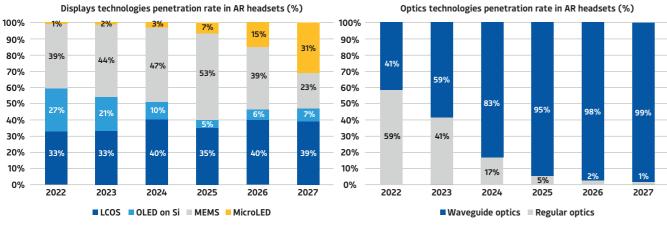

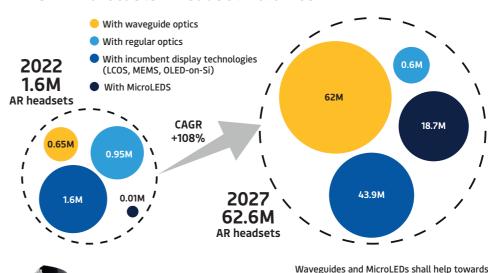

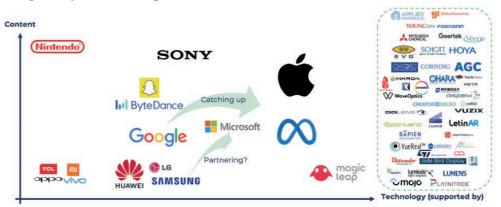

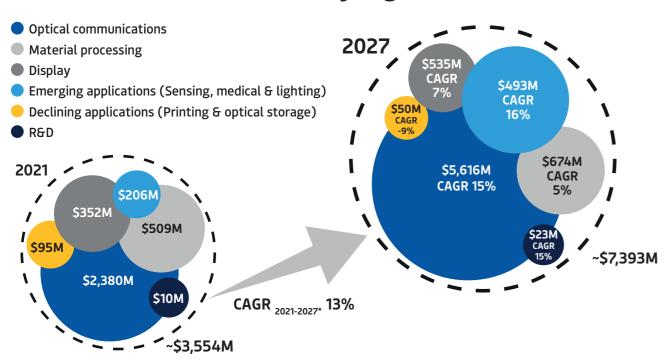

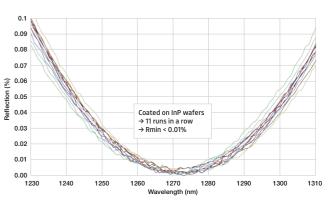

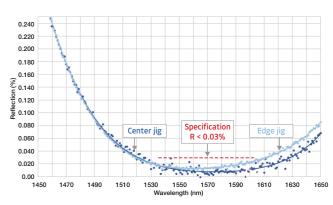

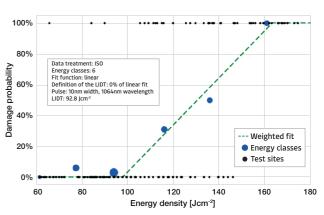

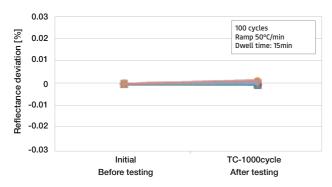

- [2] Peng et al., "Advances in SiCN-SiCN Bonding with High Accuracy Wafer-to-Wafer (W2W) Stacking Technology," 2018 IEEE International Interconnect Technology Conference (IITC), Santa Clara, CA, USA, 2018, pp. 179-181.